## **LVDS Link Tests at Birmingham**

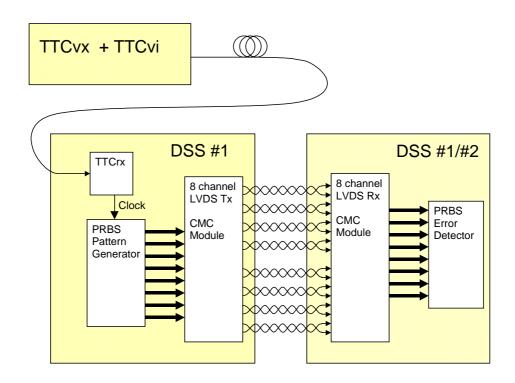

LVDS Link evaluation used the Data Source and Sink (DSS) VME modules clocked from a TTC test system:

Results using the original LVDS deserialiser DS92LV1210 operating at 40MHz (maximum frequency) showed a low tolerance to power supply noise and clock jitter. (March 2000)  $\rightarrow$

Error rates of <10<sup>-12</sup>

The original deserialisers could only be used at 40MHz provided:

- Transmitters were clocked from a high stability source.

- Cable HF loss was over-compensated.

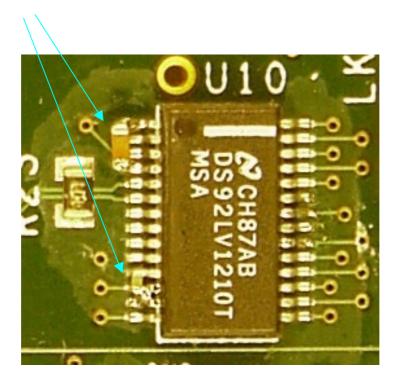

- Receiver supplies were heavily filtered:

#### Additional decoupling capacitors

But now ...

... faster LVDS chip-sets are available, operating at 40 - 66MHz word rates.

| Parameter                      | Original<br>device<br>DS92LV1210 | "High range"<br>device<br>DS92LV1224 | Upgraded "Low range" DS92LV1212A |

|--------------------------------|----------------------------------|--------------------------------------|----------------------------------|

| Frequency range                | 16 - 40MHz                       | 40 - 66MHz                           | 16 - 40MHz                       |

| Data Timing margin (min)       | 100ps                            | 450ps                                | 450ps                            |

| Receiver<br>Threshold<br>(max) | 100mV                            | 50mV                                 | 50mV                             |

| Power consumption (typ)        | 145mW                            | 191mW                                | 191mW                            |

| Latency                        | 1.75 T                           | 1.75 T                               | 1.75 T                           |

- The later devices have a much improved timing margin on incoming data when compared with the original part.

- With the newer devices available do not even consider using the DS92LV1210 device at 40 MHz

### Test results

LVDS link tests were repeated using the faster 40 - 66MHz Deserialiser part (DS92LV1224)

Several overnight tests on were run on various cable assemblies:

- 4ch. 15m of compact AMP cable 1370754-1

- 8ch. 12m of Datwyler cable.

- 4ch. 20m of Datwyler cable.

No errors were detected

3 x 10<sup>13</sup> bits were sent over each link.

# Further overnight tests

High VME activity, reading from the DSS status register:

8 ch. over 2 x 15m of AMP cable (1370754-1)

Still No errors detected > 40Hrs  $5 \times 10^{13}$  bits sent over each link.

### The new improved LVDS chipsets;

- do NOT need a high stability 40MHz clock source feeding the transmitter.

- are tolerant of supply noise. (fed from logic supply, without additional decoupling)

- allow cable equalisation to be relaxed, with particular component values now covering a much larger range of cable lengths.

Pic 'n' Mix works, but should we keep to one chip set?

|                         | '1210        | '1212A | '1024    |

|-------------------------|--------------|--------|----------|

|                         | Low range Rx |        | Hi range |

| '1021 Low range Tx -die | ×            | ?      | ✓        |

| '1023 High range Tx - ? |              |        |          |

The complimentary 40 - 66 MHz serialiser is not (yet) available in die form. → PPr MCM.

### **Further Work**

• Repeat Link Tests with system 'stressed'

- Produce LVDS Source module with Fanout:

- Heidelberg L-FAN chip

- Pericom Bus LVDS Crospoint / repeater (PI90LVB044)