## **Software Plans**

## **Murrough Landon – 23 January 2001**

http://www.hep.ph.qmw.ac.uk/~landon/talks

#### **Overview**

- Preparations for slice test

- Run controllers

- People

- Hardware

# **Slice Test Preparations (1)**

## **Specification of tests**

- Not yet defined in detail what tests we want to do

- What sets of hardware are required

- What sets of test vectors or other input data

- What software is needed to support all this

#### **Documents...**

- Should write down answers to the above

- Draft: Proposals for use of the TTC system

- Draft: Integration with Online run control

# Slice Test Preparations (2)

#### **Required Software for Slice Tests**

- System setup

- Databases: hardware configuration, calibrations, trigger menu

- Suites of test vectors

- Run control system

- IGUI panel(s)

- Hardware access library

- Data taking

- Readout/dataflow framework

- Hardware access library (again)

- Calibration procedures

- Monitoring and analysis

- More IGUI panel(s)

- Event dump

- Online monitoring

- Histogramming and displays

- Simulation of the processor

- Offline analysis?

## **Run Controllers (1)**

#### State model and hierarchy

- Run controllers make transitions between states:

- Initial

- Loaded

- Configured

- Running

- Paused

- also some superstates and error states

- Controller may have child controllers

- Parent makes transition first, then tells child controllers to do the same

- Synchronisation: either all children asynchronously "at once", or one by one in forward or reverse order

- NO private synchronisation or communication between controllers in different crates

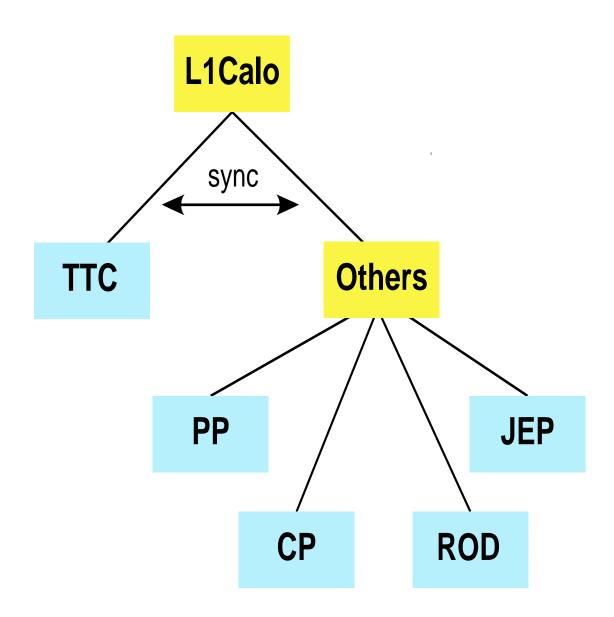

#### L1Calo Hierarchy

- We will sometimes want TTC actions before all other actions in one transition, or after all other actions.

- Implies extra layer in hierarchy for TTC

- Is this enough?

# Run Controller Hierarchy for L1Calo Slice Tests

Final system probably similar, but with more than one instance of PP, CP, JEP and ROD crates

# **Run Controllers (2)**

## **Specifications**

- Draft document on our run controller(s) in preparation

- Details of the actions required for each state transition for each crate and module

- Normal physics runs and (eventually) all types of calibration runs

#### **State Transition Overview**

- Follow recommendations from the Online group:

- Initial

Loaded: read database, establish network connections

- Loaded

Configured: configure hardware (run type independent) and software (start threaads, processes)

- Configured→Running: run type dependent stuff

- Note that the run parameters, eg run type (normal or calibration) can be changed in the Configured state, so hardware settings which may depend on the run type should only be done at the transition into the Running state

# **Run Controllers (3)**

#### **Detailed State Transition Actions**

- Initial→Loaded:

- Read hardware configuration for crate

- Create run time objects for modules

- Lock resources against simultaneous use by other partitions

- Loaded→Configured:

- FIRST: use TTC broadcast to sync LVDS links?

- Check expected modules are actually present

- Can load any run type independent settings into modules

- Configured→Running:

- Load run type dependent settings into modules

- LAST: for some calibrations, use TTC broadcast to start synchronous playback

- Periodically (maybe separate thread or process?):

- Read status, error counts, PP rates

- Publish in the information service

## Workplan and people

## Slide from last meeting...

A rough outline of tasks required for the slice tests was discussed at our recent UK software meeting. Some names have been pencilled in...

• Test vectors: Bill

Readout and related stuff: Bruce

• Run control: Murrough

• Database: Murrough

• Histo displays: Norman/Steve

• Monitoring (readout out): Bruce

Monitoring (user end): Steve (and Bill?)

• Event Dump: Steve

• Calibration: ?

The assumption was that Cornelius would be available for maintaining and developing HDMC (with input from Bruce). Not sure who will maintain HDMC in future...

## **Hardware**

#### **Crate CPUs**

- Three more Concurrent Technologies CPUs will (have?)

been ordered, same as the one at QMW

- Mainz have two VME PCs, one similar to ours

- Heidelberg expect to have their home grown solution

- Slice tests require about five or six crates

- Status of CPU "personality cards" for 9U crates?

## **ATLAS Readout System on a PC**

- Still awaiting PC ROS solution from CERN...

- ...meanwhile, have we ordered the Slink bits?

- Look into PCI bridge for multi Slink setup (slice tests: 2 PPRODs, 6 CPRODs)

- ROD crate DAQ development scheduled for 1 April