# JEM SOFTWARE

#### Thomas Trefzger

Jürgen Thomas, Cano Ay, Marc Unverzagt

University of Mainz, Germany

### **EXISTING SOFTWARE**

- Configure FPGAs

- Load DSS buffer memories

- Load and read playback, spy memory

- Load, read and write, compare test vectors

Problem: Shell scripts directly calling VME driver utilities

#### **FRAMEWORK**

- 2 Concurrent CPUs with either VME LINUX or CERN VME driver

- PC with RedHat Linux 7.3

All existing software is running with both drivers on all CPUs.

On all CPUs the relevant software packages are installed (ATLAS online software, HDMC, CMT, CVS,...)

#### PROBLEM...

Using a different VME driver means rewriting existing software...

Simple shell scripts are not an elegant solution...

## **SOFTWARE MODULES (HDMC)**

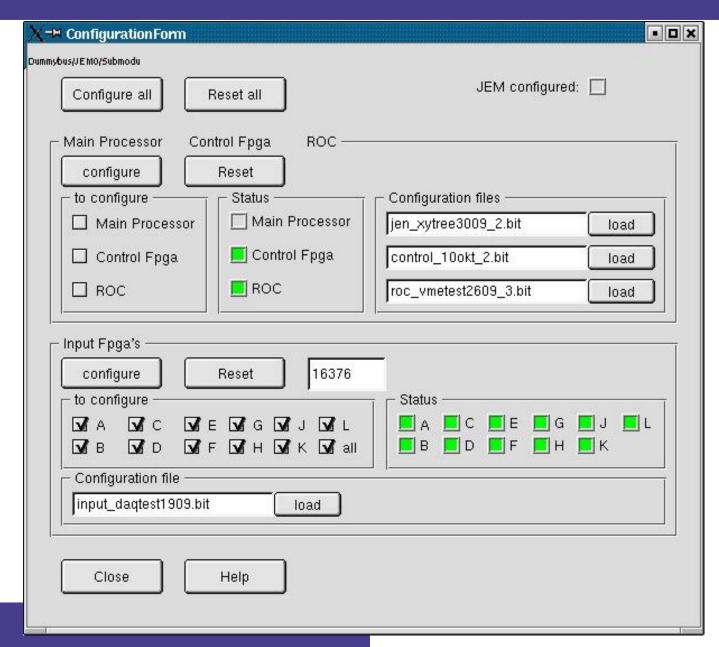

| X-™ ConfigurationForm  |                |                       | - 0 ×       |

|------------------------|----------------|-----------------------|-------------|

| Dummybus/JEMO/Submodu  |                |                       |             |

| Configure all Rese     | et all         | JEM configured:       |             |

| Main Processor Control |                |                       | Ï           |

| to configure S         | Status         | Configuration files   | <del></del> |

| ☐ Main Processor ☐     | Main Processor | jen_xytree3009_2.bit  | load        |

| ☐ Control Fpga ☐       | Control Fpga   | control_10okt_2.bit   | load        |

| □ ROC □                | ROC            | roc_vmetest2609_3.bit | load        |

| Input Fpga's           |                |                       |             |

Cano Ay, new PhD student:

Started with Gilles FpgaXilinxJEM file,

Program to configure control FPGA, main processor and ROC

### **SOFTWARE MODULES (HDMC)**

Cano Ay, new PhD student:

Started with Gilles FpgaXilinxJEM file,

Program to configure control FPGA, main processor and ROC

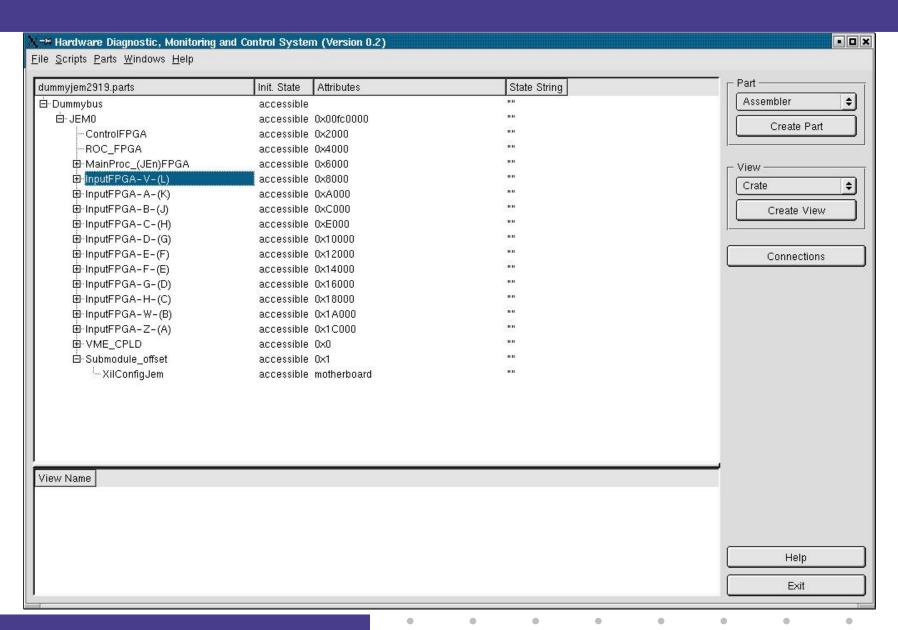

### **REGISTERS (HDMC)**

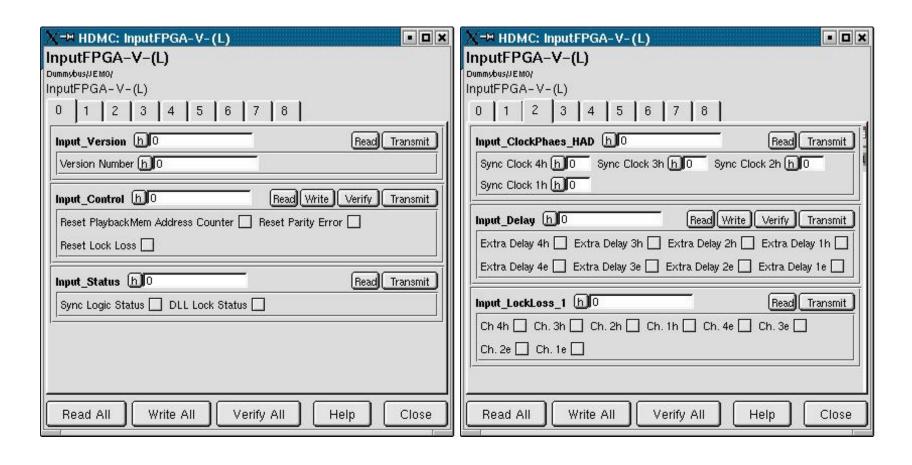

### **INPUT FPGAs (HDMC)**

#### **NEXT STEPS**

- Convert all existing software packages to HDMC and module services

- Next step: Integrate lookup tables, Link status, parity errors

- Then: Test vectors

- Expected to be finished end of November

- If possible we would like to work together for a couple of days in November with UK software people.

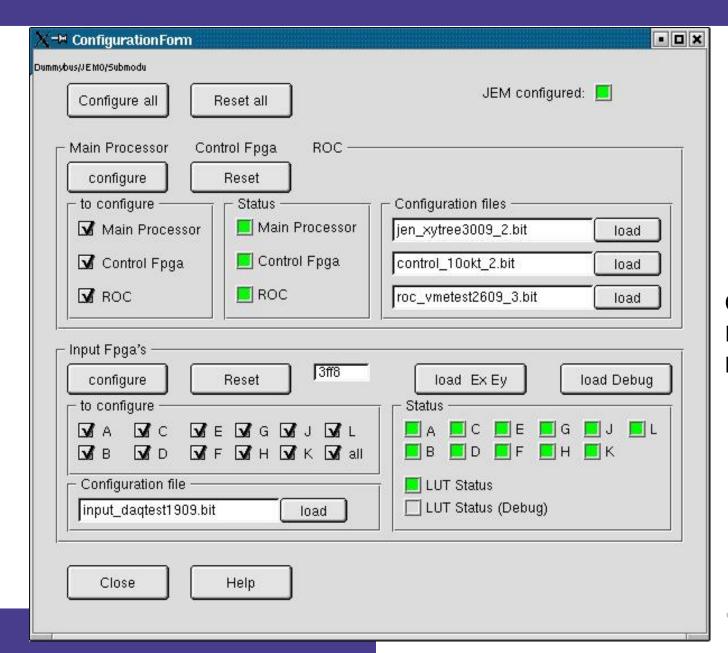

### **SOFTWARE MODULES (HDMC)**

Cano Ay, new PhD student:

LUT included

#### Status

Difficult to DEBUG HARDWARE and to WRITE SOFTWARE at the same time.

Good news: PhD student who can work most of his time on software development

### **SUBSLICE TEST**

- CPU from Mainz

- Online software if possible in HDMC/module services format

- Otherwise use existing shell script software

All new software will be written in HDMC/module services framework.