# **JEMO (\*)**

- JEMO Hardware: overview, history, and status

- JEM0 Firmware: algorithms, status

- JEM plans and timescale

(\*) Module0 specifications: last update draft 0.8d (Nov.13, 2001) http://www.physik.uni-mainz.de/schaefer/browsable/JemSpecsFinal

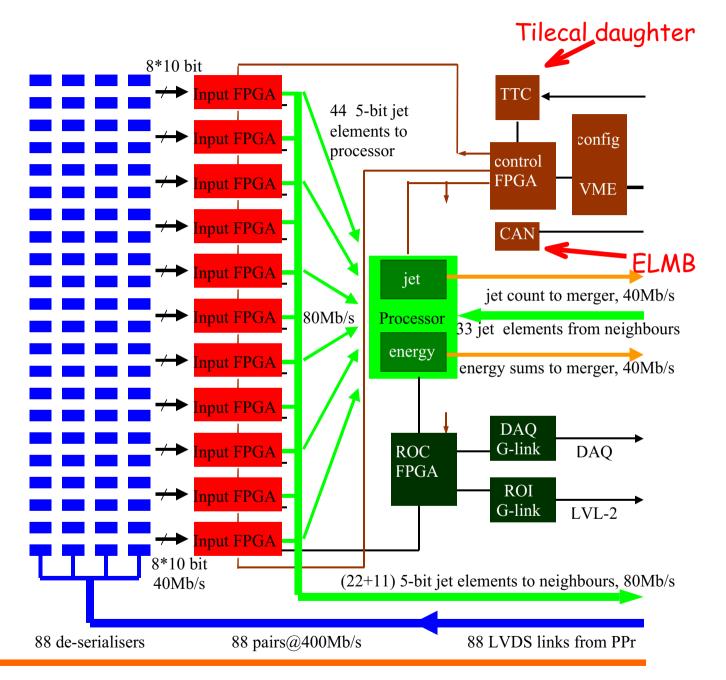

# JEM -Block Diagram-

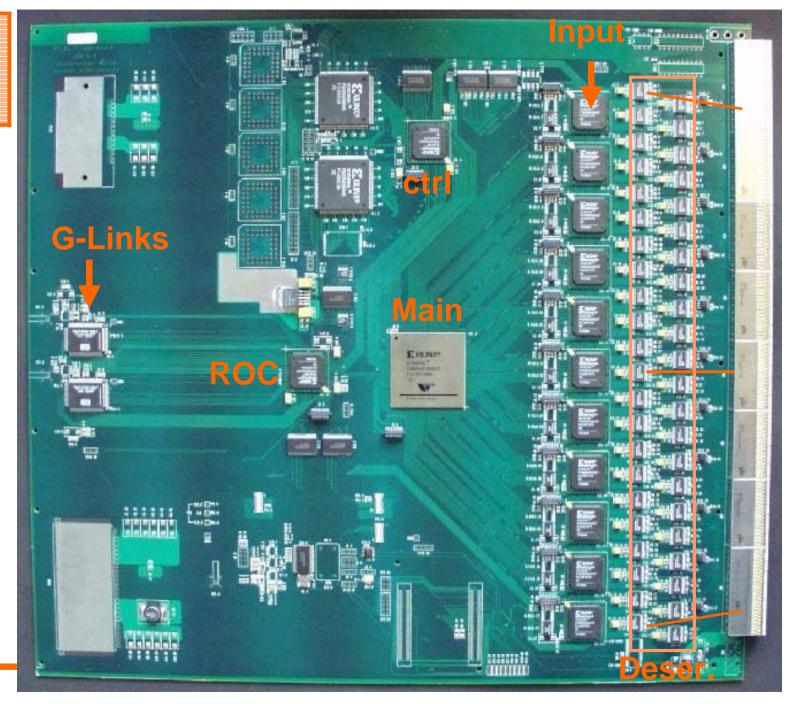

# JEMO.0 -top view-

## the JEMO production saga

```

board design files to PCB manufacturer (Andus)

02.01.2001

PCB production fails, 2nd run required

module 0.0 assembly (Mair) utter failure, re-work required

XC2S150 fail (non-documented power-down) -> re-work again

-- Nov. 2001 : joint meeting (RAL) --

05.11.2001

order a new PCB (module 0.1) from Andus

PCB delivered. Electrical test & impedance test (at Andus): ok.

22.11.2001

module 0.0 back from re-work. Looks ugly. Requires re-rework

01.12.2001

in our lab. Backplane connectors still not well aligned.

send module 0.1 to Rohde & Schwarz for assembly & test.

14.11.2001

module 0.1 back from assembly (X-rayed at R&S: ok).

16.01.2002

Module looks good. No obvious connectivity problems.

```

-- 2 months assembly time include 1 month waiting for tantalums to arrive –

Both modules powering up successful. Starting first tests...

### the JEMO hardware status

The current module was designed to **moduleO** specifications. Therefore it is considered a fully functional module with full channel count. Some **implementation details** are considered non-final and should be revised before start of mass production, if possible.

#### **Known** issues:

TTC interface missing (availability of daughter bd.)

DCS interface missing/non-final

Very scarce logic resources on main processor

Logic resources on input FPGAs

#### resolve:

before slice test before and after before or/and after after slice test

#### And at lower priority:

| Improvement of B/Scanability (de-serialisers,)                                                                                             | ?   |   |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|---|

| Coherence of TTCrx control (HW?) Coherence of DCS sub-system Coherence of FPGA configuration mechanisms (HW?) Simplification of VME access | ? ? |   |

|                                                                                                                                            |     | ? |

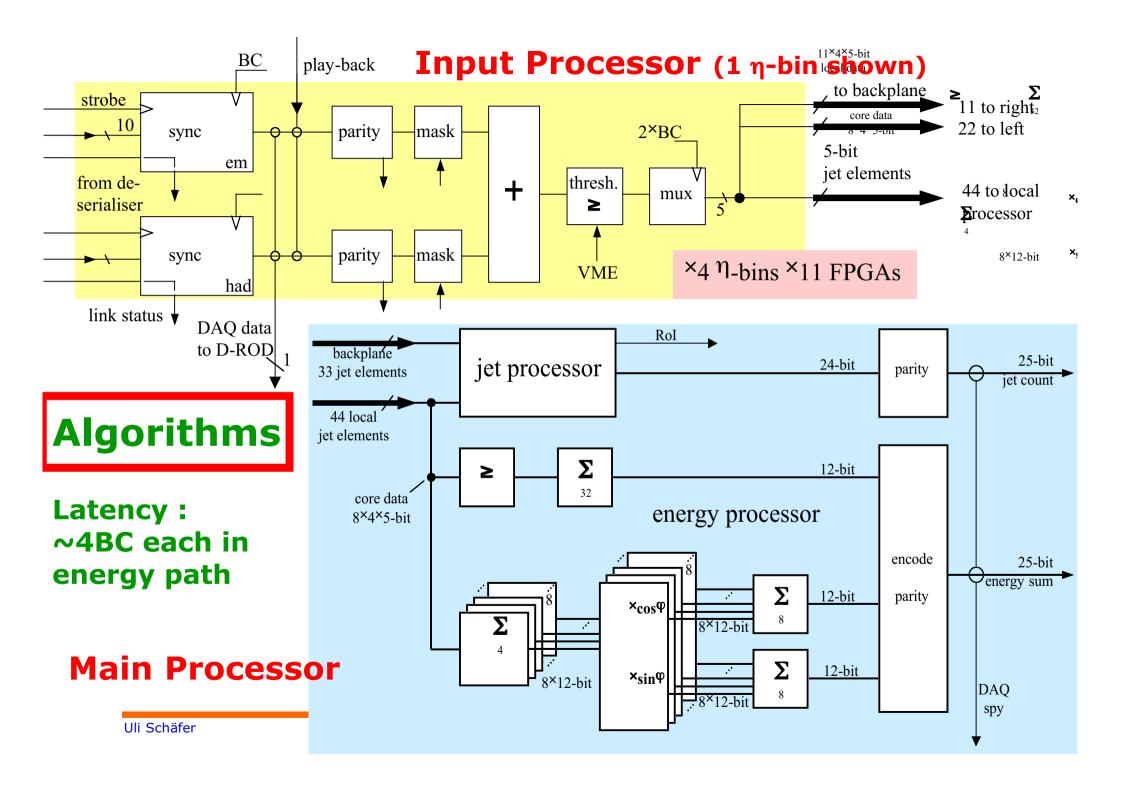

## Firmware Status

- VME CPLD carries a basic VME interface including FPGA-configuration download port

- Input FPGA almost finished. Input synchronisation derived from the CP code at an early stage, might require update.

- Main processor: Top level and energy processor almost finished. Need to instantiate jet processor. FCAL handling will have to be modified due to revised allocation of FCAL channels.

- Control FPGA lacks TTC interface

- ROC code still incomplete, Andrea working on that.

- Modifications to VME control path (see next slide)

## JEM0 test status Hard-/Firmware

- JEM0.0: No systematic connectivity tests after last re-work. use module (as is) as a test-bed for firmware (Andrea) Problems discovered with VME access. Timing?

- → Convert all FPGA control code (main processor, ROC) to fully synchronous, using I/O flip-flops

- → Convert input FPGA control code (RDO ring bus!) to synchronous where possible.

Prepare HW (DSS) and SW for test of real-time data path (Thomas)

JEM0.1: Try to systematically test connectivity, using JTAG/BS (Bruno)

Test equipment: JTAG Technologies PM3705 Explorer + VIP automatic test generation.

requires endless exception lists due to large count of non-BS ´able devices → avoid use of non-BS ´able components in future designs, don't expect connectivity test results too soon!

## Considerations for next iteration

JEM0.1 looks good (though connectivity test results are not yet available).

- Assembly of 9Ux40cm modules is nontrivial and expensive, but possible.

- We need to improve testability. JTAG/BS seems useful only if most of the components are B/scannable. Be careful with choice of components for next iteration. Fortunately scannable LVDS describilisers are available now.

- BGA re-work equipment is expensive and we might rather rely on services from the private sector.

- It is not yet clear whether there is any advantage of standard pitch vs. fine pitch components. Cheapest currently listed high-pin count (624 User-I/O), 1.28mm pitch BGA is XC2V2000-4BF957C at \$860. That's ok for main processor. For input FPGAs etc. standard pitch (XC2V1000-4BG575) will cost an additional \$126,000 total! That's unacceptable. This means input processor daughterboards will be required if we want to rule out fine pitch BGAs on 9U Modules.

## Plans / timescale

#### Slice test - summer 2002:

- JEM0.1 hardware ready to go into slice test unless connectivity problems found in ongoing tests

- ELMB and TTCrx daughter (to be built) need to be integrated

- A lot of work required on firmware and software

- After successful standalone tests, 2 further JEM0s need to be manufactured (possibly with larger main processor chips, XCV1000E). This will take ~ 1 month if all components are available and if the current economic situation persists

#### **Future plans**

We need to decide on improvements on de-serialisers (JTAG/BS), processor FPGAs, and CAN. If overall timescale slips, we might decide to design a new module early on, so as to avoid major board revisions immediately before start of mass production.