## **DSS** Firmware Updates

## James Edwards RAL

ATLAS-UK Level-1 Calorimeter Trigger Meeting 18th June 2002

### Introduction

- Contents of PCO 001.

- Designs affected.

- Problems \* / Solutions.

- \* Also known as "*Design Features*".

- Design Verification in R25 HDL.

- Future Modifications.

## Project Change Order - 001

This was finally signed off on 9th May 2002 and work commenced.

Item 1

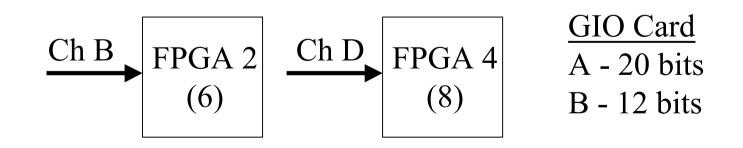

- Use dual-port memory (DPRAM) as a test source for testing other variants of ROD firmware.

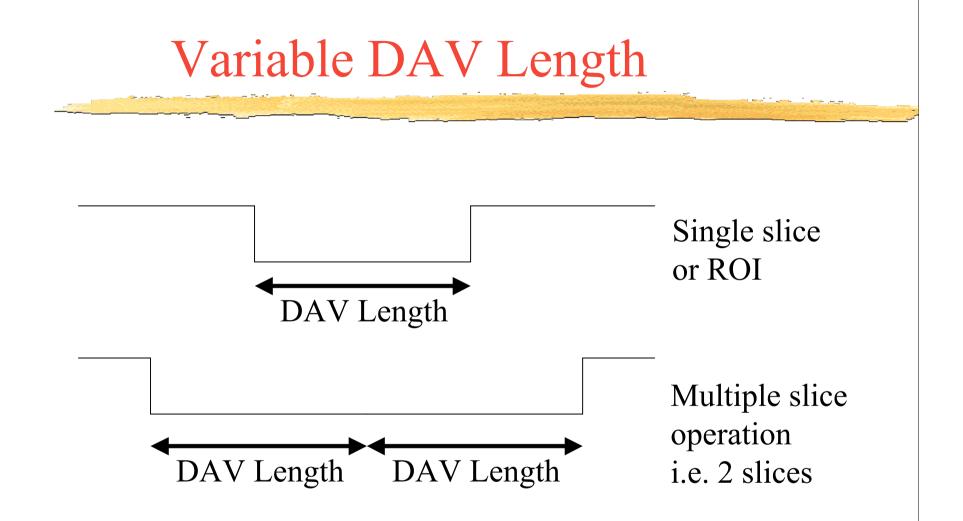

- This requires a programmable register to control the length of the DAV signal.

Item 2

DPRAM read/ write 32 bit words and automatic comparison test of 32 bit words to use with the general purpose I/O CMC (GIO).

### Item 3

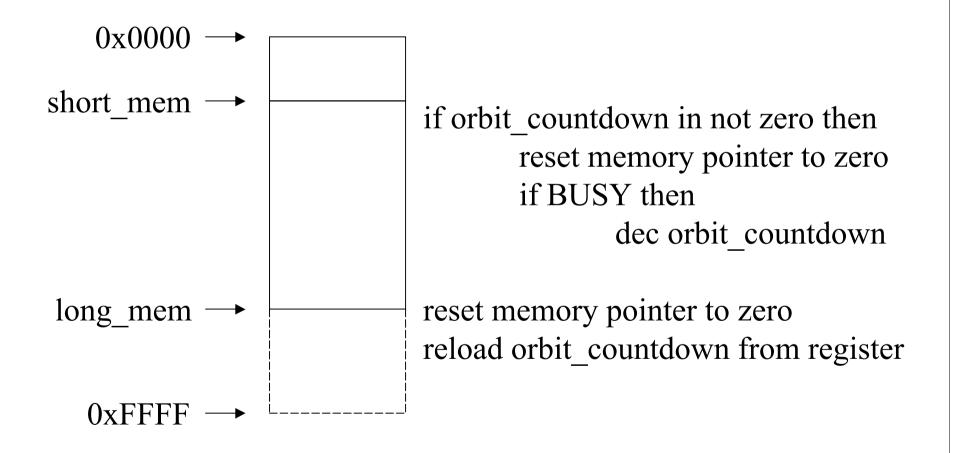

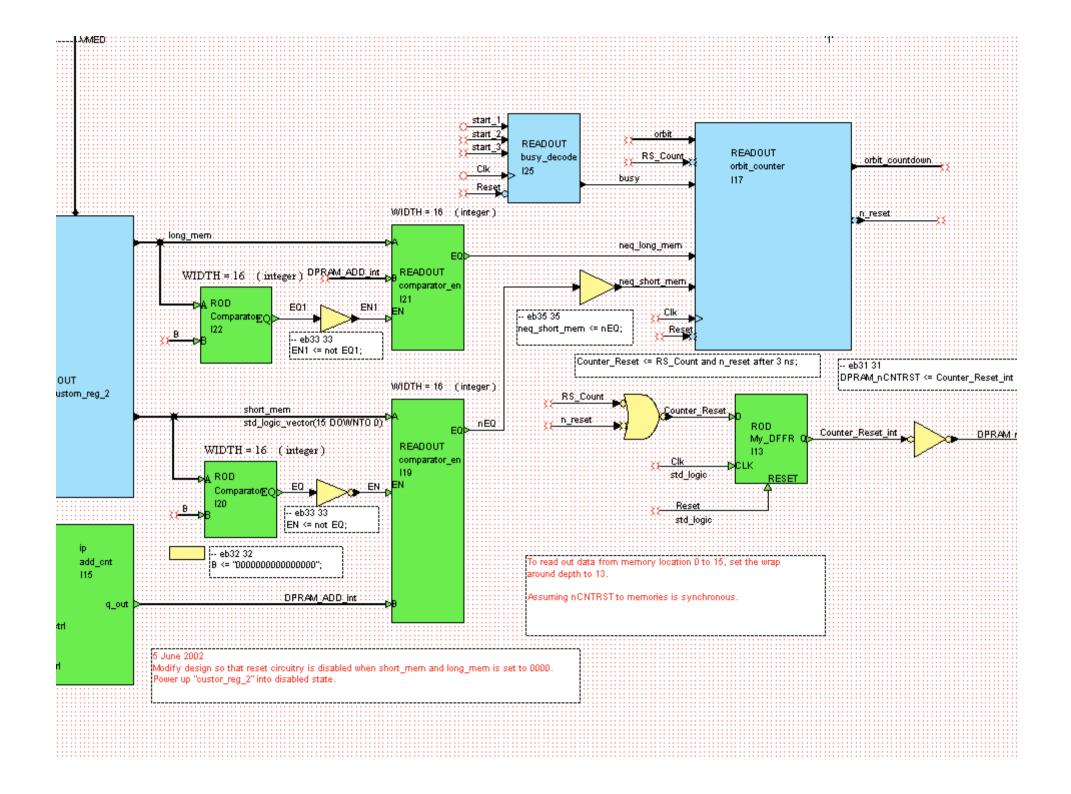

**32K** wraparound on the DPRAMs to be changed to a programmable depth. The DSS will require two programmable comparators "short mem" (16 bit) and "long mem" (16 bit) to determine the memory addresses at which wraparound to zero occurs, plus a programmable "orbit" register and an orbit countdown counter (32 bit).

a.

On reset (on power-up and "Address Counter Reset"), "orbit" is copied to "orbit\_countdown" and mem\_address is set to 0.

b.

The memory address is incremented each 25 ns. The DSS now plays the memory contents through the GIO daughter board.

- C.

- When memory\_address reaches short\_mem AND orbit\_countdown is non zero, mem\_address is reset to 0. If the front panel BUSY input is present, orbit\_countdown is decremented by 1 (This is the end of a single orbit data set).

d.

When memory\_address equals long\_mem, mem\_address is reset to 0 and orbit\_countdown is reloaded from "orbit". (This is the end of a multiple-orbit data set)

### Designs to Modify

Item 1

Change for "ROD Test Source".

Items 2 and 3

Modification for the GIO daughter card.

This is basically the LVDS cards design of old.

Required changes to both the Transmitter (Item 3) and Receiver (Item 2).

# Additional Modification 1

- The Xilinx CPLD on the DSS required modification in order to cope with the increased number of registers.

- Created decoding for an extra 2 registers in each Data FPGA.

- Also added the capability of an additional 2 registers in the SLINK FPGA's.

## Additional Modification 2

The routing of the "BUSY" signal to the DATA FPGA's was required.

This signal is an input to the Altera CPLD only. The use of sending this signal out on a *spare* pin was prohibited as all spare capability between the Altera CPLD and the DATA FPGA's was already being used.

#### SERIOUSLY BAD NEWS... THINK AGAIN

The Fix

Devised a scheme where the "BUSY" signal was encoded onto a pre-existing net. Used the "start" net.

- Start pulsing LOW for 25 ns signals the system is BUSY.

- Start pulsing LOW for 50 ns signals that the system is NOT BUSY.

# Update DSS CPLD's

- So far only DSS's with serial numbers 01 and 03 have been updated CPLD's.

- Others MUST be updated before using with latest firmware.

## ROD Test firmware

The "ROD Test" firmware now has a new version/type code of 0216 hex.

- DAV length register is at the following addresses:-

- Daughter Card 1:-

- 108,10C, 110 and 114. (hex)

- Daughter Card 2:-

- 118,11C, 120 and 124. (hex)

- The DAV length register (8 bit) powers up to 84 decimal. i.e. Slice Data.

# Design Verification

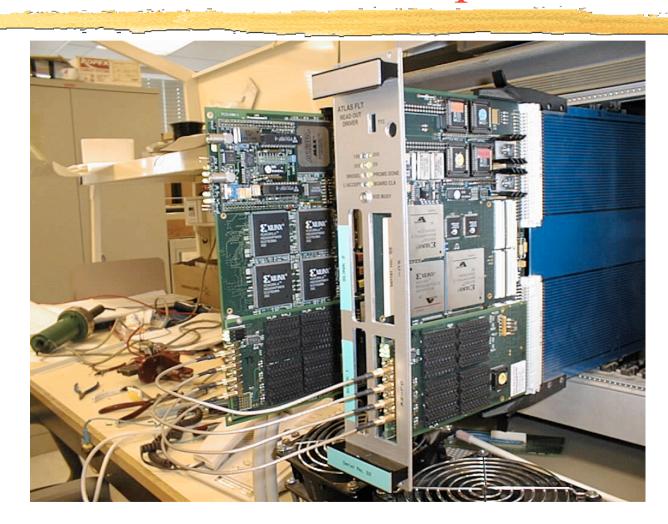

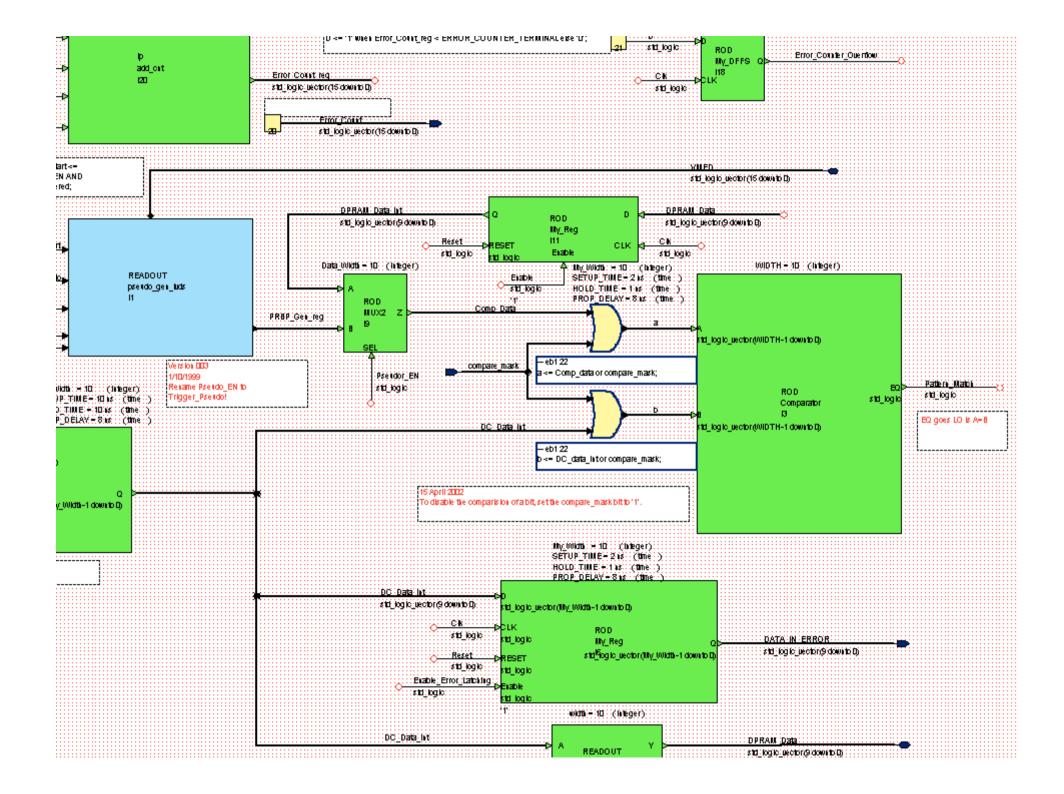

- Performed limited tests in R25 HDL using DSS and ROD with the Glink Tx and Rx cards.

- Results indicated that basic data transfer was still working.

- Release firmware to Bruce on 28<sup>th</sup> May 2002 for extensive tests.

- At time of writing have not received any complaints.

## ROD Test Setup

ATLAS-UK Level-1 Calorimeter Trigger Meeting 18th June 2002

## GIO daughter card - New versions

- The new LVDS Source for GIO has version/type code of "0612" hex.

- The new LVDS Sink for GIO has version/type code of "0A13" hex.

# GIO daughter card - Source 1

Orbit register (32 bits) is at:Daughter Card 1:108,10C, 110 and 114. (hex)

Daughter Card 2:118,11C, 120 and 124. (hex)

#### Note

This occupies the same address space as DAV register in "ROD test" design.

# GIO daughter card - Source 2

Long mem / Short mem

bits 31 - 16 / bits 15 - 0

Registers at addresses:Daughter Card 1:

130,134, 138 and 13C. (hex)

Daughter Card 2:

140,144, 148 and 14C. (hex)

# Memory Diagram

# Possible Problems / Design Features

- The design relies upon the counter in the FPGA keeping track with the address counter in the memory chips.

- Due to latency in the design short\_mem and long\_mem should be set to a value of 2 less than the last data memory location required.

## Design Features Continued...

- Setting both long\_mem and short\_mem to 0x0000 will disable the RESET mechanism and allow rollover at 32k as normal.

- After loading the orbit\_countdown register you should apply an "Address Counter Reset" to ensure that the value is transferred to the orbit\_countdown counter.

# GIO daughter card - Sink 1

Compare Mask (20 bits)

Daughter Card 1:

108,10C, 110 and 114. (hex)

Daughter Card 2:

118,11C, 120 and 124. (hex)

# GIO Daughter Card - Sink 2

Set bit high to disable the comparison of that data bit.

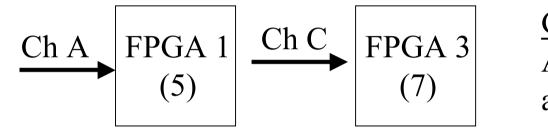

- This allows the GIO data width of 32 bits to run within a design that originally allowed a data with of 80 bits (Previous daughter cards such as Glink or LVDS has data widths of 4x20).

- FPGA 1 (5) 20 bits

- FPGA 2 (6) 12 bits

• () indicate Daughter card in slot 2.

### Automatic Comparison

<u>Glink Cards</u> A, B, C and D are 20 bits.

# Design Verification

- Performed limited tests in R25 HDL using RAMP data and LOOPBACK card.

- Results seemed to indicate that the RESET mechanism was working as expected.

- Firmware ready for release for extensive tests in R1 on 27<sup>th</sup> May 2002.

# GIO Test Setup

ATLAS-UK Level-1 Calorimeter Trigger Meeting 18th June 2002

### Firmware on WWW

| Device Firmware        | Current Version | Modification Date | Comments                             |

|------------------------|-----------------|-------------------|--------------------------------------|

| • VME Decoder          | 6               | 28/05/2002        |                                      |

| • <u>VME Registers</u> | 16              | 28/05/2002        | Add additional register<br>decoding. |

| © LVDS Source          | 6               | 28/05/2002        | © Pseudo Ramp Source                 |

| © LVDS Sink            | 10              | 28/05/2002        | © <u>Pseudo Ramp Sink</u>            |

| © <u>G-Link Source</u> | 10              | 7/12/2000         |                                      |

| © G-Link Destination   | 11              | 10/8/2000         |                                      |

| © <u>S-Link Source</u> | 5               |                   |                                      |

| © S-Link Destination   | 6               | 23/10/2000        |                                      |

| C ROD Test             | 2               | 28/05/2002        | Use with Glink Tx card               |

$http://www.te.rl.ac.uk/local/ESDG/SDG/Projects/atlas-flt/external/firmware\%20 folder/dss/firmware.html \label{eq:local}$

# Additional Requests 1

It has been suggested that these additional registers cause problems with the diagnostic software as different cards have different register space, requiring a different module definition file for each combination of daughter cards.

"Solution" is to add extra un-used registers.

## Additional Requests 2

If required, additional r/w registers can be added.

- This could affect up to 6 designs so is not a trivial task.

- Don't mention the 6 1/2 hours required to add a divide by 2 circuit to the 40 MHz clock to the CP chip for Richard.

### Compromise

- Have agreed to add "dummy" registers to all future DSS Data FPGA designs.

- This modification will not be released until I am required to change a design for "technical" reasons.

# Acknowlegements

### Summary

- 5 designs modified in total.

- Basic tests in R25 HDL indicate that PCO 001 has been completed.

- Require further extensive testing in R1.