# **Project Specification**

# Project Name: ATLAS Level-1 Calorimeter Trigger-Read-out Driver

Version: 1.1

## 17 Jan 2007

| Approval        | Name           | Signature | Date |

|-----------------|----------------|-----------|------|

| Project Manager | V. J. O Perera |           |      |

| Customer        | C. N. P Gee    |           |      |

Authors: B. M Barnett, C. N. P. Gee, V. J. O. Perera

# Distribution for all updates:

Project Manager:

Customer:

C. N. P. Gee

Group Leader responsible for Project:

R. N. J. Halsall

Project Design Engineers

J. Edwards

W. Qian

Project Managers of related projects:

B. M. Barnett

R. Staley P. Hanke U. Schäfer S. Silverstein

Account Manager: S.P.H. Quinton

Level-1 Calorimeter Trigger Project manager E. Eisenhandler

This document will evolve as the detailed design advances.

# **Contents**

| 1 | Introdu | ction                                       | 9  |

|---|---------|---------------------------------------------|----|

|   | 1.1 Dat | a transmission overview                     | 9  |

|   | 1.2 RO  | D data handling                             | 10 |

|   | 1.3 Dat | a sources and content                       | 11 |

|   | 1.4 Mai | nagement of output S-Links                  | 11 |

|   |         | a-rate limitation                           |    |

|   | 1.6 Org | anisation of ROD Modules                    | 12 |

| 2 | _       | cal Aspects of the ROD Module               |    |

|   |         | ctional Requirements                        |    |

|   |         | dout Process                                |    |

|   | 2.2.1   | DAQ readout (slice) data                    |    |

|   | 2.2.2   | Single- and Multiple-timeslice data         |    |

|   | 2.2.3   | Format of S-Link Event Fragments.           |    |

|   | 2.2.4   | G-Link Timeout                              |    |

|   | 2.2.5   | G-Link DAV Gap.                             |    |

|   | 2.2.6   | Trigger Type Timeout                        |    |

|   | 2.2.7   | Handling S-Link Link Full                   |    |

|   | 2.2.8   | Handling ROD Busy                           |    |

|   | 2.2.9   | Event Counter and Event Counter Reset       |    |

|   | 2.2.10  | RoI Data                                    |    |

|   |         | a Transfer Rates in the ROD                 |    |

|   | 2.3.1   | G-Link input data rates                     |    |

|   | 2.3.2   | Maximum Trigger Rates                       |    |

|   | 2.3.3   | S-Link output data rates                    |    |

|   | 2.4 S-L | ink Mapping                                 |    |

|   | 2.4.1   | RoI Data from CPM, JEM, and CMMs            |    |

|   | 2.4.2   | DAQ Data from Preprocessor, CP and JEP      |    |

|   | 2.5 Zer | o suppression and compression.              |    |

|   | 2.5.1   | Zero suppression                            |    |

|   | 2.5.2   | Compression                                 | 27 |

|   | 2.6 Dat | a Replay Mode                               |    |

| 3 |         | nal blocks                                  |    |

|   |         | ical Inputs                                 |    |

|   | 3.2 G-I | ink                                         | 28 |

|   | 3.3 Inp | ıt FPGA                                     | 28 |

|   | 3.4 Swi | tch FPGA                                    | 28 |

|   | 3.4.1   | Event Selection and Sampling                |    |

|   | 3.4.2   | TTC-correlated Event Selection and Sampling |    |

|   | 3.4.3   | Bunch Crossing Number Buffer                |    |

|   | 3.4.4   | Event Number Buffer                         |    |

|   | 3.4.5   | Trigger Type Buffer                         |    |

|   | 3.4.6   | Orbit Number Buffer                         |    |

|   | 3.4.7   | Status Words                                |    |

|   | 3.4.8   | Status Count                                |    |

|   | 3.4.9   | Data Count                                  |    |

|   | 3.4.10  | Checkpoint Handling                         |    |

|   |         | ink                                         |    |

|   | 3.5.1   | S-Link Hardware Interface                   |    |

|   |         | D S-Link Packet                             |    |

|   |         |                                             |    |

|   | 3.6.1    | Format Version Numbers                 | 33 |

|---|----------|----------------------------------------|----|

|   | 3.6.2    | Module Identifiers                     | 33 |

|   | 3.6.3    | Subdetector Identifier                 | 34 |

|   | 3.6.4    | Run Number and Run Type                | 34 |

|   | 3.6.5    | Detector-Specific Event Type           | 34 |

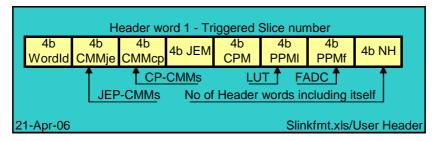

|   | 3.6.6    | User Header                            | 34 |

|   | 3.7 Cal  | ibration and Monitoring                | 35 |

|   | 3.7.1    | Monitoring FPGA.                       | 35 |

|   | 3.7.2    | Instruction RAM                        | 35 |

|   | 3.7.3    | Dual-Port RAM                          | 35 |

|   | 3.7.4    | PCI Interface                          | 35 |

|   | 3.7.5    | Auxiliary Front-Panel Output           | 36 |

|   | 3.8 VM   | IE Interface                           | 36 |

|   | 3.8.1    | Interrupt Capability                   | 37 |

|   | 3.9 TTC  | Crx Decoder Card                       | 37 |

|   |          | NBus                                   |    |

|   |          | et, Reload, and Module Initialisation  |    |

|   | •        | tem ACE                                |    |

|   | 3.13 Usi | ng Replay Mode                         | 39 |

|   | 3.13.1   | Input FPGA Settings for Replay         |    |

|   | 3.13.2   | Switch FPGA Settings for replay        | 40 |

|   | 3.14 Mo  | therboard                              | 40 |

|   | 3.14.1   | Signal Handling on the Motherboard     | 40 |

|   | 3.14.2   | Front Panel Input and Outputs          |    |

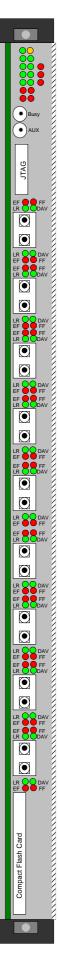

|   | 3.14.3   | Front Panel Monitoring (LEDs)          |    |

|   | 3.14.4   | Rear Panel Input and Outputs           | 42 |

|   | 3.14.5   | Test and Set-up Points                 | 42 |

|   | 3.14.6   | Ground Points                          |    |

|   | 3.14.7   | Power Requirements from VME            |    |

|   | 3.14.8   | Crate Power Requirements               |    |

| 4 | _        | mming Model                            |    |

|   |          | delines                                |    |

|   |          | ation                                  |    |

|   |          | dressing Modes                         |    |

|   |          | mory Map for CR/CSR space              |    |

|   | 4.4.1    | VME64-Defined Configuration ROM        |    |

|   | 4.4.2    | VME64x Defined Configuration ROM       |    |

|   | 4.4.3    | VME64 Defined CSRs                     |    |

|   | 4.4.4    | VME64x Defined CSRs                    |    |

|   | 4.4.5    | User Control & Status Registers (CSRs) |    |

|   |          | mory Map for Normal VME space          |    |

|   |          | therboard Register Map.                |    |

|   | 4.6.1    | Module Number Register                 |    |

|   | 4.6.2    | Control Mode Register                  |    |

|   | 4.6.3    | Control Pulse Register 1               |    |

|   | 4.6.4    | Control Pulse Register 2               |    |

|   | 4.6.5    | Addressing Control Register            |    |

|   | 4.6.6    | Status Register 1                      |    |

|   | 4.6.7    | Status Register 2                      |    |

|   | 4.6.8    | Interrupt Register                     |    |

|   | 4.6.9    | VME CPLD firmware revision no.         | 53 |

| 4.6.10                     | VME FPGA firmware revision no.                       | 53  |

|----------------------------|------------------------------------------------------|-----|

| 4.6.11                     | CAN Access Register A                                | 54  |

| 4.6.12                     | CAN Access Register B                                | 54  |

| 4.6.13                     | TTCrx Control Register                               | 54  |

| 4.6.14                     | TTCrx Status Register                                | 55  |

| 4.6.15                     | TtcI2cId Register                                    | 55  |

| 4.6.16                     | Ttc Broadcast Data Register                          | 56  |

| 4.6.17                     | TTC DQ Register                                      | 56  |

| 4.6.18                     | TTC Dump RAM                                         | 56  |

| 4.7 Inp                    | out FPGA Register Map                                | 57  |

| 4.7.1                      | Input FPGA Common Version                            | 58  |

| 4.7.2                      | Input FPGA Status Register                           | 58  |

| 4.7.3                      | Input G-Link Error Map                               | 59  |

| 4.7.4                      | Input G-Link Error Count                             | 60  |

| 4.7.5                      | Input Control Pulse Register                         | 60  |

| 4.7.6                      | Input Data FIFO Busy Depth                           | 61  |

| 4.7.7                      | Input Event Management FIFO Busy Depth               | 61  |

| 4.7.8                      | Input BCN FIFO Busy Depth                            | 61  |

| 4.7.9                      | Input Channel Version Number                         | 62  |

| 4.7.10                     | Input Channel Control Register                       | 62  |

| 4.7.11                     | Input Channel Status Register                        | 63  |

| 4.7.12                     | Input Channel Expected Slice Count                   | 63  |

| 4.7.13                     | Input Channel Subslice Control Register              | 64  |

| 4.7.14                     | Input Channel Compression Control Register           | 64  |

| 4.7.15                     | Input Channel Source ID Register                     | 65  |

| 4.7.16                     | Input Channel Neutral ID                             | 65  |

| 4.7.17                     | Input Channel Event Management FIFO address pointers | 66  |

| 4.7.18                     | Input Channel Bunch Number FIFO address pointers     | 66  |

| 4.7.19                     | Input Channel Data FIFO address pointers             | 66  |

| 4.7.20                     | Input Channel FIFO Depth Monitor Registers           | 67  |

| 4.7.21                     | Input Channel Event Management FIFO Access           | 67  |

| 4.7.22                     | Input Channel Bunch Number FIFO Access               | 67  |

| 4.7.23                     | Input Channel Data FIFO Access                       | 67  |

| 4.8 Sw                     | vitch FPGA Register Map                              | 68  |

| 4.8.1                      | Switch FPGA Revision                                 | 70  |

| 4.8.2                      | Switch Control Register                              | 70  |

| 4.8.3                      | Switch FPGA Pulse Register                           | 71  |

| 4.8.4                      | Switch FPGA Status Register                          | 71  |

| 4.8.5                      | Run Number Register                                  | 72  |

| 4.8.6                      | ECR Count Register                                   | 72  |

| 4.8.7                      | Replay BCN Register                                  |     |

| 4.8.8                      | Replay Event Number Register                         | 72  |

| 4.8.9                      | Replay Trigger Type Register                         | 73  |

| 4.8.10                     | TTC SampleId Register                                | 73  |

| 4.8.11                     | RoI Wordlimit Register.                              |     |

|                            | S-Link Control Register                              | 73  |

| 4.8.12                     | 73                                                   |     |

|                            | S-Link Status Register                               | 7.4 |

| 4040                       | _                                                    | /4  |

| 4.8.13                     | 74                                                   |     |

| 4.8.13<br>4.8.14<br>4.8.15 | _                                                    | 75  |

|   | 4.8.16 | Spy Status Register                                | 75  |

|---|--------|----------------------------------------------------|-----|

|   | 4.8.17 | Trigger Type Timeout Register                      | 76  |

|   | 4.8.18 |                                                    |     |

|   | 4.8.19 | BCN FIFO Pointer Register                          | 76  |

|   | 4.8.20 | e e e e e e e e e e e e e e e e e e e              |     |

|   | 4.8.21 | Detector Event Type Register                       |     |

|   | 4.8.22 | 7.2                                                |     |

|   | 4.8.23 |                                                    |     |

|   | 4.8.24 | <u> </u>                                           |     |

|   | 4.8.25 |                                                    |     |

|   | 4.8.26 | <u> </u>                                           |     |

|   | 4.8.27 | <u> </u>                                           |     |

|   | 4.8.28 | 8 71                                               |     |

|   | 4.8.29 | <del>_</del>                                       |     |

|   | 4.8.30 | <del>_</del>                                       |     |

|   | 4.8.31 | S-Link 0-3 LFF time                                |     |

|   | 4.8.32 |                                                    |     |

|   | 4.8.33 |                                                    |     |

|   | 4.8.34 | <u> </u>                                           |     |

|   | 4.8.35 | 1,                                                 |     |

|   |        | 1.0                                                |     |

|   | 4.9 M  | onitoring FPGA Register Map  Monitor FPGA Revision |     |

| 5 |        |                                                    |     |

| 3 |        | s of DAQ and RoI data and formatseneral guidelines |     |

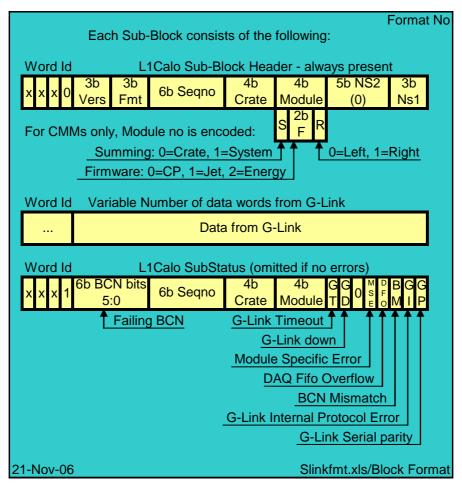

|   |        | verall Sub-block format                            |     |

|   |        | eutral S-Link format                               |     |

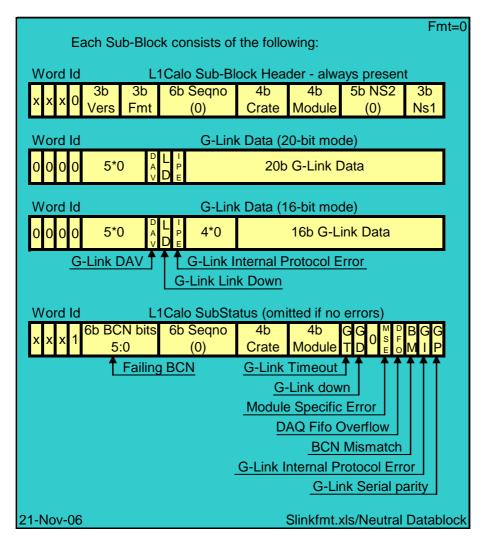

|   | 5.3.1  | Output S-Link DAQ data Format (Fmt=0)              |     |

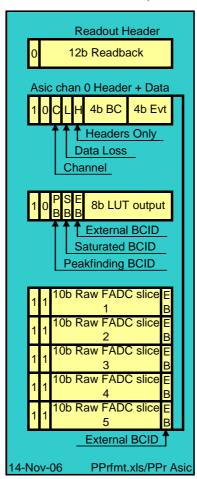

|   |        | eprocessor DAQ data                                |     |

|   | 5.4 F1 | Input G-Link DAQ data format                       |     |

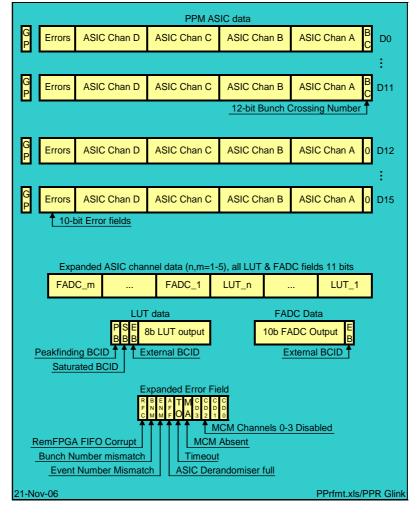

|   | 5.4.1  | General Structure of PPM S-Link Data.              |     |

|   |        |                                                    |     |

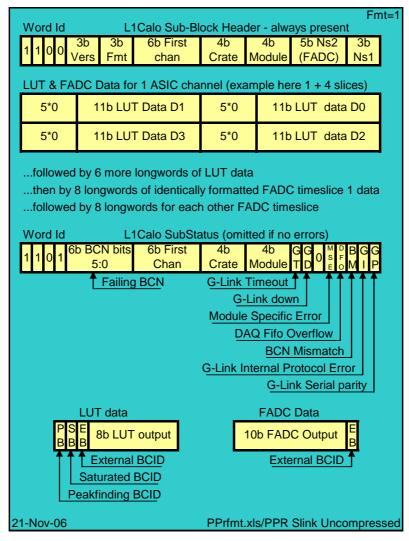

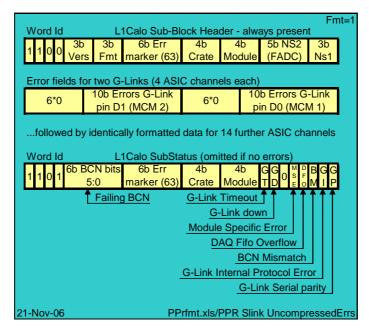

|   | 5.4.3  | Uncompressed S-Link DAQ output format. (Fmt = 1)   |     |

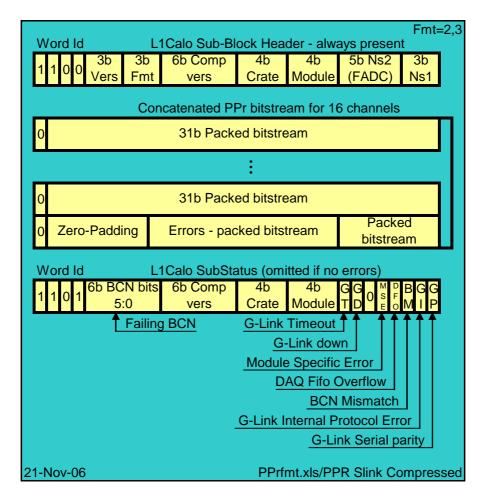

|   | 5.4.4  | Compressed S-Link DAQ output format. (Fmt = 2)     |     |

|   | 5.4.5  | Super-Compressed S-Link DAQ output format (Fmt=3)  |     |

|   |        | PM DAQ Data                                        |     |

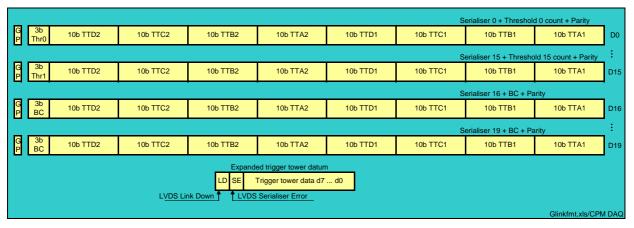

|   | 5.5.1  | Input G-Link DAQ data format.                      |     |

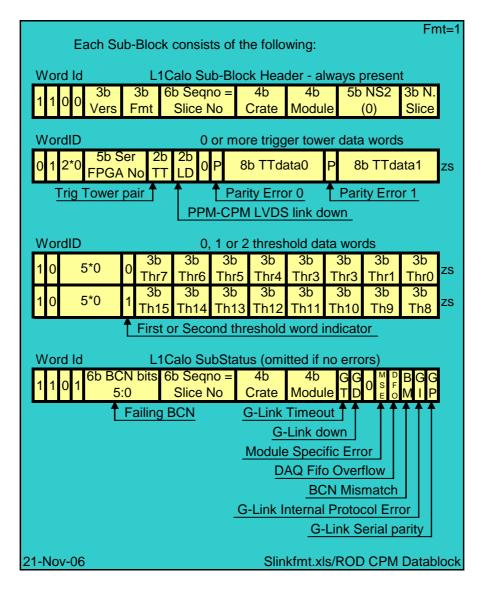

|   | 5.5.2  | Output S-Link DAQ data format (Fmt=1)              |     |

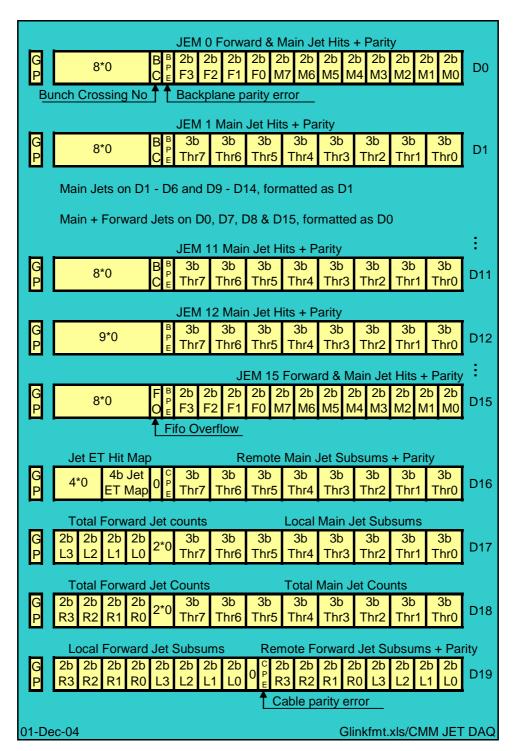

|   |        | EM DAQ Data                                        | 95  |

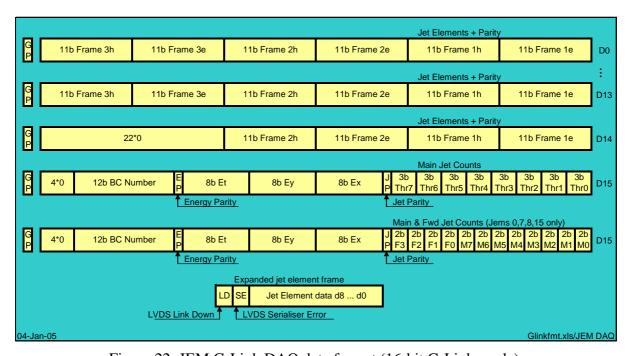

|   | 5.6.1  | Input G-Link DAQ data format                       |     |

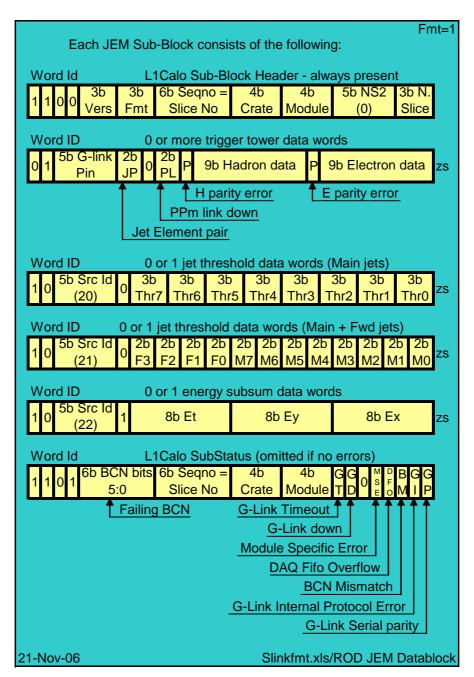

|   | 5.6.2  | Output S-Link DAQ data format (Fmt=1)              |     |

|   |        | MM-CP DAQ                                          |     |

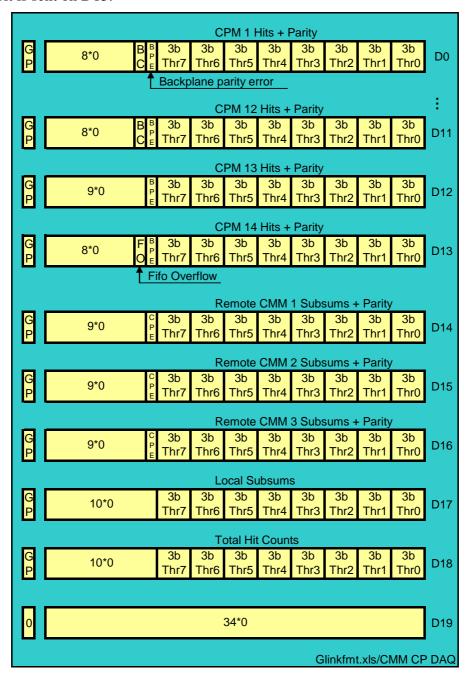

|   | 5.7.1  | Input G-Link DAQ data format.                      |     |

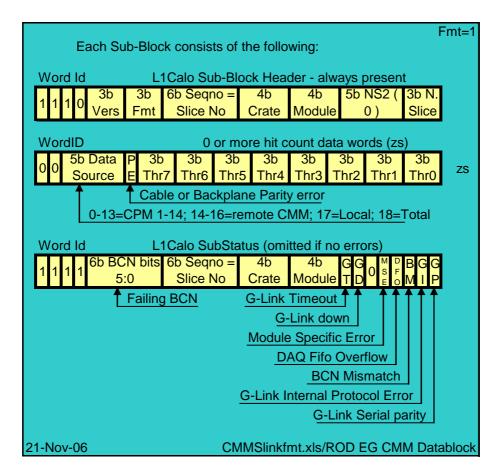

|   | 5.7.2  | Output S-Link DAQ data Format (Fmt=1)              |     |

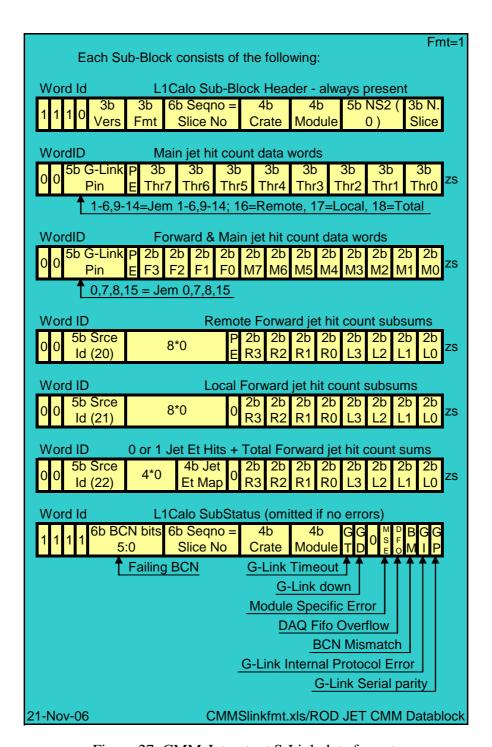

|   |        | MM-Jet DAQ                                         |     |

|   | 5.8.1  | Input G-Link Data format                           |     |

|   | 5.8.2  | Output S-Link DAQ data Format                      |     |

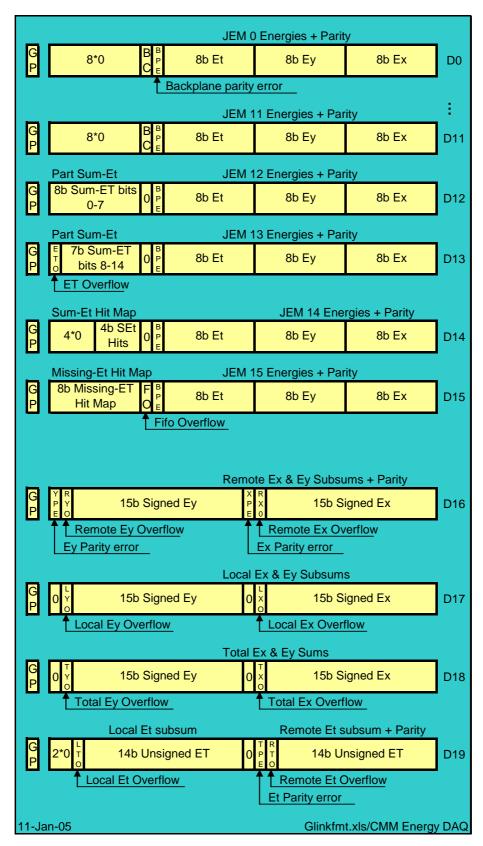

|   |        | MM-Energy DAQ                                      |     |

|   | 5.9.1  | Input G-Link DAQ Data format                       |     |

|   | 5.9.2  | Output S-Link DAQ data format                      |     |

|   |        | eneral features of RoI Formats                     |     |

|   |        | PM RoI Data                                        |     |

|   | 5.11.1 | Input G-Link RoI data format                       | 104 |

|   | 5.11.2 Output S-Link RoI format                            | 105 |

|---|------------------------------------------------------------|-----|

|   | 5.12 JEM Jet RoI                                           | 106 |

|   | 5.12.1 Input G-Link RoI data format                        | 106 |

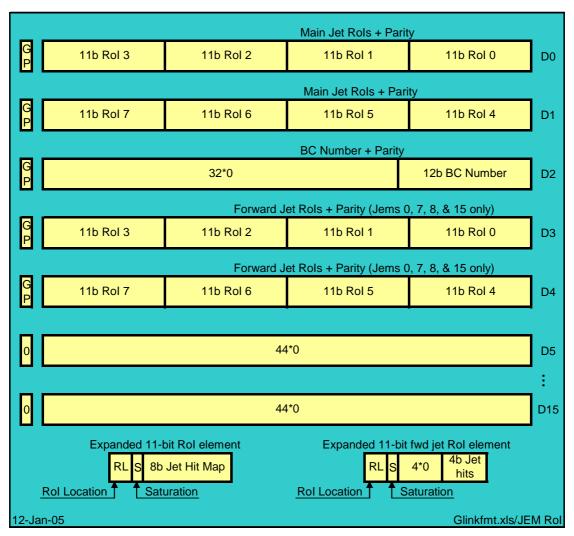

|   | 5.12.2 Output S-Link RoI data format                       | 106 |

|   | 5.13 CMM-Jet-E <sub>T</sub> RoI                            |     |

|   | 5.13.1 Input G-Link Data format                            | 107 |

|   | 5.13.2 Output S-Link RoI data Format                       |     |

|   | 5.14 CMM-Energy RoI                                        |     |

|   | 5.14.1 Input G-Link Data format                            |     |

|   | 5.14.2 Output S-Link RoI data Format                       |     |

|   | 5.15 S-Link Status word formats                            |     |

| 6 |                                                            |     |

|   | 6.1 Manufacturing                                          |     |

|   | 6.2 Testing                                                |     |

|   | 6.2.1 Test Strategy                                        |     |

|   | 6.2.2 Test equipment                                       |     |

|   | 6.3 Software                                               |     |

|   | 6.4 Installation                                           |     |

|   | 6.5 Maintenance and further orders                         |     |

| 7 |                                                            |     |

|   | 7.1 Personnel                                              |     |

|   | 7.2 Project Responsibilities                               |     |

|   | 7.3 Deliverables                                           |     |

|   | 7.4 Project plan (Milestones)                              |     |

|   | 7.5 Design Reviews                                         |     |

|   | 7.6 Training                                               |     |

|   | 7.7 CAE                                                    |     |

|   | 7.8 Costs and finance.                                     |     |

|   | 7.9 Intellectual Property Rights (IPR) and Confidentiality |     |

|   | 7.10 Safety                                                |     |

|   | 7.11 Environmental impact                                  |     |

|   | 7.11.1 Disposal                                            |     |

|   | 7.11.2 EMC                                                 |     |

|   | 7.12 Handling Precautions.                                 |     |

| 8 |                                                            |     |

| 9 |                                                            |     |

|   | 9.1 Version 1.0 (Post-review):                             |     |

|   | 9.2 Version 1.05                                           |     |

|   | 9.3 Version 1.06                                           |     |

|   | 9.4 Version 1.07                                           |     |

|   | 9.5 Version 1.08                                           |     |

|   | 9.6 Version 1.09                                           |     |

| A | S-link rear transition module Connector Pin-out            |     |

|   | A.1 5-row P2 connector map to two S-LINK LSCs              |     |

|   | A.2 5-row P3 connector map to two S-LINK LSCs.             |     |

| A | Appendix B VME 64x J0 Connector Pin Assignment             |     |

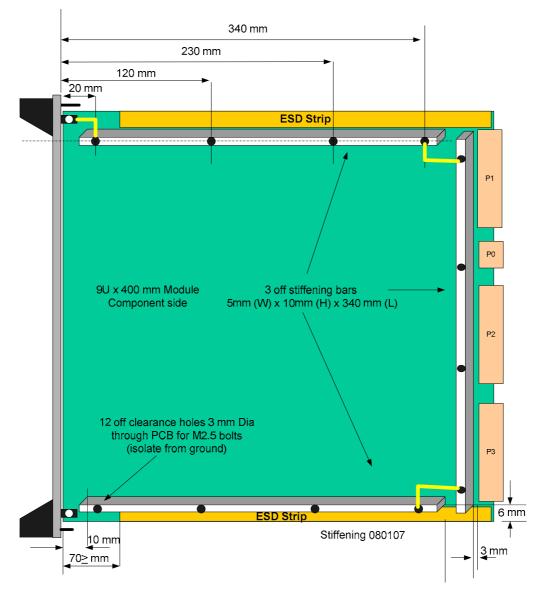

|   | nnendiy C Stiffening and ESD strip details for 911 ROD     |     |

# **List of Figures**

| Figure 1: Overview of a typical data readout scheme                                 | 9    |

|-------------------------------------------------------------------------------------|------|

| Figure 2: Use of DAV* to frame valid G-Link data.                                   | 10   |

| Figure 3: Organisation of ROD input links and crates, showing one of two ROD crates | 13   |

| Figure 4: ROD module with S-Link rear transition module                             | 13   |

| Figure 5: ROD Block Diagram                                                         | 15   |

| Figure 6: Overall structure of event fragment payload (CPM, JEM, and CMM data)      | 18   |

| Figure 7: Overall structure of event fragment payload (PPM data)                    |      |

| Figure 8: Timing sequence of signals related to Event Counter Reset                 | 21   |

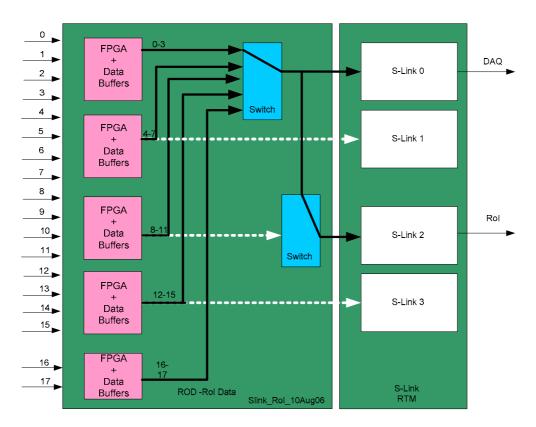

| Figure 9: RoI S-Link mapping, showing active (solid) and unused (dashed) data paths | 24   |

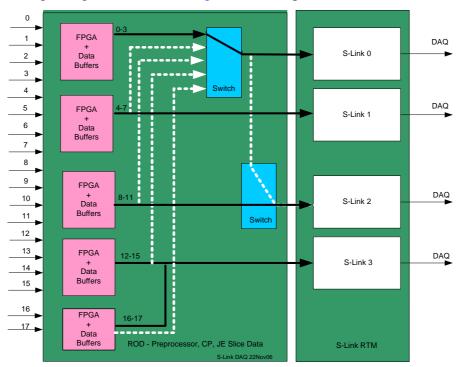

| Figure 10: DAQ data S-Link mapping for JEP crates.                                  | 25   |

| Figure 11: Rear S-Link Transition Module                                            | 32   |

| Figure 12: Format of User Header                                                    | 35   |

| Figure 13: Overall S-Link Sub-Block format.                                         | 83   |

| Figure 14: Neutral S-Link format.                                                   |      |

| Figure 15: Bitstream format from one PPM ASIC channel                               | 87   |

| Figure 16: PPM Input G-Link data format                                             | 89   |

| Figure 17: Uncompressed PPM S-Link output DAQ format                                | 91   |

| Figure 18: Uncompressed PPM S-Link output DAQ format - error block                  | 91   |

| Figure 19: PPM Compressed S-Link DAQ data format                                    | 92   |

| Figure 20: CPM G-Link DAQ data format                                               | 93   |

| Figure 21: CPM S-Link DAQ data format                                               | 94   |

| Figure 22: JEM G-Link DAQ data format (16-bit G-Link mode).                         | 95   |

| Figure 23: JEM S-Link DAQ data format                                               | 96   |

| Figure 24: CMM-CP G-Link DAQ data format                                            | 97   |

| Figure 25: CMM-CP S-Link DAQ data format                                            | 98   |

| Figure 26: CMM-Jet input G-Link DAQ format                                          | 99   |

| Figure 27: CMM-Jet output S-Link data format.                                       | .100 |

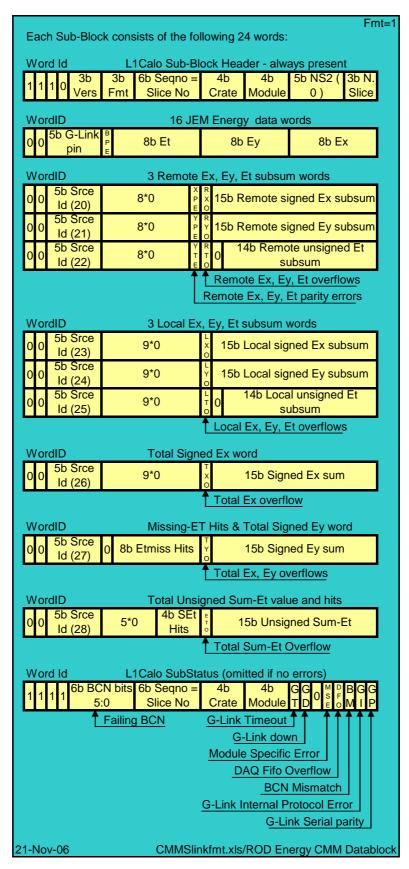

| Figure 28: CMM-Energy G-Link DAQ input format                                       | .101 |

| Figure 29: CMM-Energy Output S-Link DAQ data format                                 | .103 |

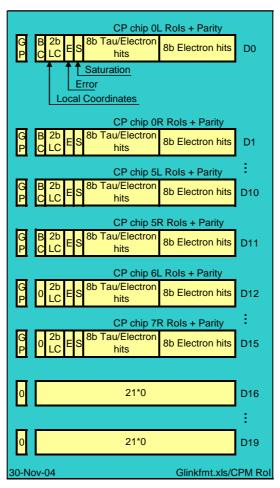

| Figure 30: CPM G-Link RoI data format.                                              | .104 |

| Figure 31: S-Link RoI data formats                                                  | .105 |

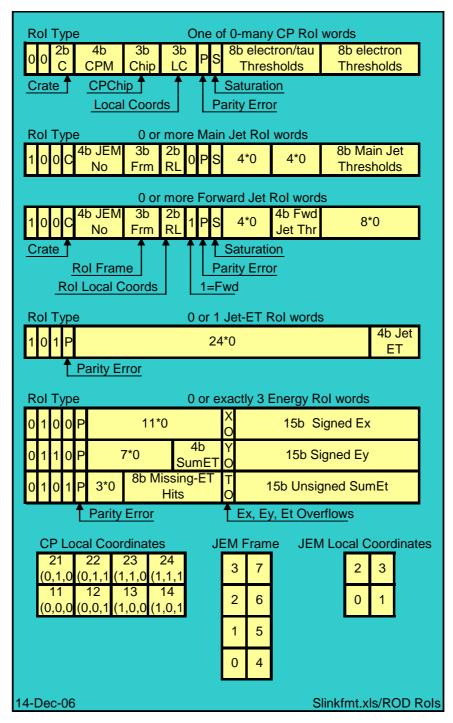

| Figure 32: Jet RoI G-Link format (16-bit G-Link mode)                               | .106 |

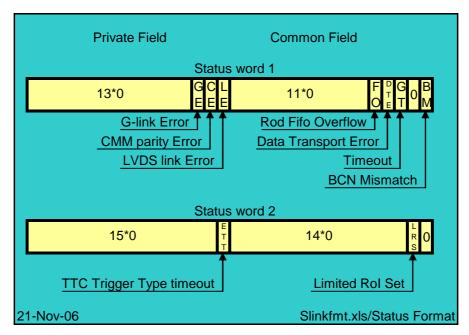

| Figure 33: Format of S-Link status words.                                           |      |

| Figure 34: Stiffening and ESD strip details for 9U ROD.                             | .118 |

|                                                                                     |      |

# **List of Tables**

| Table 1: Numbers of RODs and S-Links                                              | 12 |

|-----------------------------------------------------------------------------------|----|

| Table 2: ROD data sources and firmware types                                      | 16 |

| Table 3: G-Link data rates into RODs                                              | 22 |

| Table 4: Estimated S-Link Data Rates from each ROD                                | 23 |

| Table 5: G-Link use for RoI Data                                                  | 25 |

| Table 6: G-Link use for DAQ data                                                  | 26 |

| Table 7: ATLAS ROD Event Fragment, Version 3.0                                    | 33 |

| Table 8: Module identifier fields.                                                |    |

| Table 9: Allocation of ROD addresses in both ROD crates. Other slots are not used | 37 |

| Table 10: System Ace standard firmware collections.                               | 39 |

| Table 11: VME64x CR/CSR space                                                     | 44 |

| Table 12: Word-Id Values for Formatted Data                                       |    |

| Table 13: Word-Id Values for Neutral Data                                         | 82 |

| Table 14 : Sub-block header fields.                                               |    |

| Table 15: Sub-status word fields.                                                 | 85 |

# 1 Introduction

This document describes the read-out driver (ROD) module for the ATLAS Level-1 Calorimeter Trigger processor. The specification is for the final production modules.

The Level-1 Calorimeter Trigger system [1] consists of a sequence of modules which generate the level-1 trigger bit patterns used by the Central Trigger Processor (CTP) [2] to form the level-1 trigger. In addition to forming the trigger, each stage of the electronics – Preprocessor Modules (PPMs) [3], Cluster Processor Modules (CPMs) [4], Jet/Energy Modules (JEMs) [5], and Common Merger Modules (CMMs) [6] – provides ancillary readout which can be used to check the trigger performance. These data are destined for the Readout Subsystem (ROS), a part of the ATLAS DAQ system, and are referred to in this document as "DAQ" data. Additionally, CPMs, JEMS, and some CMMs provide Region-of-Interest (RoI) information, which are sent via the RoI-Builder (RoIB) to the level-2 section of the higher-level trigger system. Copies of the RoI data are also sent, for checking, to the ROS.

The ROD module described in this document provides the data formatting, compression, buffering, and change of transmission standards needed to collect the DAQ and RoI data and forward them to the ROS and RoIB.

#### 1.1 Data transmission overview

Data arrive at the RODs on optical links using a serial format generated by the G-Link chipset from Agilent [7]. The transmitting G-Link encodes 16 or 20 bits of user data into a 20 or 24-bit frame which it transmits serially at 800 or 960 Mbaud. The effective data transfer rate is 640 or 800 Mbit/s. The G-Link receiver recovers the clock and user data from the serial data stream, and also checks the framing bits to verify link stability. Where a transmitting module needs less than the full bit width of the G-Link, zero data are sent and the unused data pins may be grounded. On reception, data from unused pins are discarded, depending on the data format in use.

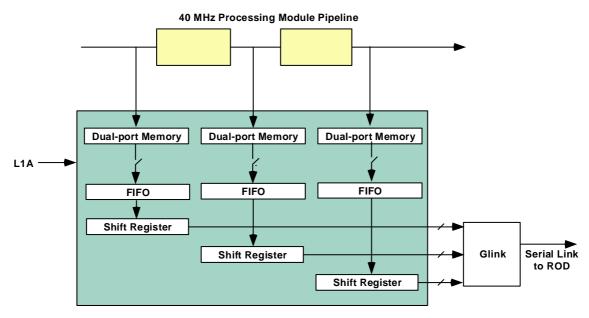

Figure 1: Overview of a typical data readout scheme

As illustrated in Figure 1, the readout process is initiated by the Level-1 Accept (L1A) signal generated by the CTP and distributed by the Timing, Trigger and Control (TTC) system [8]. All processing modules copy data from their 40.08 MHz pipelines into dual-port scrolling

ROD Specification: File ROD-spec-version1\_1.doc Page 9 of 118

memories. On receipt of an L1A signal, each module extracts data from its scrolling memories into FIFOs to await readout. Each FIFO is connected via a shift register to one of the G-Link user data pins. Logic on the module moves data from the FIFOs into the shift registers, asserts the Data Available (DAV\*) signal to the G-Link, and transmits the shift register contents for the event concerned. This typically involves sending one bit for each shift register on every G-Link clock edge. An odd parity bit is appended to each active G-Link pin when the shift register contents have been sent. The module finally deasserts DAV\* and G-Link returns to its quiescent state for at least one clock cycle. During quiescent periods, the transmitting G-Link sends fill frames (FF1) to maintain the lock between the transmitter and receiver.

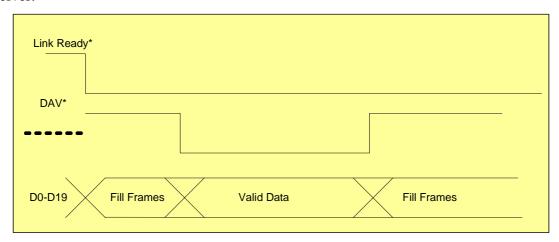

Figure 2: Use of DAV\* to frame valid G-Link data.

The DAV\* signal is used by the transmitting end to frame the serial data streams, and is recovered by the receiving G-Link device on the ROD. Data reception is initiated at the ROD end when the DAV\* becomes active. Up to 18 G-Links may be active on the ROD simultaneously receiving data. If for any reason one of the expected DAV\* signals is not received, that particular link times out (see section 2.2.4) and data from the other links are sent on to the DAQ or RoIB as normal.

When the link is down, the output DAV\* signal from the receiving G-Link oscillates as it tries to establish lock. To avoid confusion in the logic, the received DAV\* is qualified by the Link Ready\* signal before being used to extract the data from the G-Link.

# 1.2 ROD data handling

In the ROD, the transition from quiescent to active state of the receiving G-Link is signalled by the assertion of the receiver DAV\* signal. The G-Link receiver presents the recovered 40 MHz clock and parallel 16- or 20-bit user data at its output. Firmware in the ROD collects, processes and stores the data in 32-bit-wide FIFOs with the format of the output event record. The conversion process includes checks of parity and Bunch-Crossing Number (BCN) as well as zero-suppression or data compression. The ROD also receives the L1A signal via the TTC subsystem, shortly followed by the event trigger type needed in the ATLAS ROD fragment header. When all required information has been received from the TTC and G-Links, the ROD assembles a complete ATLAS event fragment with header, payload from G-Links, and trailer, and sends the completed fragment to the ATLAS readout subsystem.

ROD Specification: File ROD-spec-version1\_1.doc Page 10 of 118

### 1.3 Data sources and content

In normal use, each ROD processes either DAQ data only or RoI data only. The data input, processing, and output are significantly different in the two cases.

The DAQ readout data are intended for trigger monitoring and calibration, and include information collected near to the processing module inputs and outputs. These data, extracted parasitically from the 40.08 MHz pipelines, are associated in time with particular clock cycles and therefore with particular LHC bunch crossings, and are referred to as "timeslices". All processing modules can sample a programmable number of consecutive timeslices. The minimum spacing between L1As means that a maximum of five timeslices can be read out in normal physics running, although longer readout is needed for calibration with the PPM. The time offset of the readout relative to the L1A may be programmed via registers in the modules. When all modules are properly configured, the data derived from a specified LHC bunch crossing may be tracked through the complete trigger system. Readout of multiple timeslices is useful in setting up and checking the internal digital timing of the trigger, and is essential to verify the correct operation of bunch crossing identification with the long calorimeter pulses.

RoI data are read out only for the single timeslice corresponding to the L1A. They provide the Level-2 trigger with information about the spatial position of e.m. and hadronic clusters and jets, and total and missing transverse energy measured in the calorimeters.

Full details of all data content and formats may be found in section 5.

# 1.4 Management of output S-Links

The ROD module is equipped with four S-Links to transmit the output data to the ROS and RoIB. The S-Link specification [9] defines a FIFO-like electrical interface providing data transport at up to 160 Mbyte/s per link, with flow control, status, and error detection signals. Several physical implementations of the interface exist.

The volume of RoI data handled by a ROD is typically a few percent of the S-Link bandwidth. A single S-Link carries the RoI data from an RoI ROD to the RoIB, and a second S-Link carries a copy to the ROS. The remaining two links are unused on RoI RODs.

For a ROD handling DAQ data, the data volume depends on the L1A rate, the occupancy of the detector (hence the LHC luminosity and background), the number of timeslices being read out, and the type and effectiveness of the zero-suppression or data compression algorithms. Some of these parameters are hard to predict, so the ROD must include configuration options to use from one to four S-Links to despatch the output data. All DAQ S-links go only to the ROS. At high data rates, the input G-Link data volume may temporarily exceed the bandwidth of the S-Links, and buffers are provided to smooth the data flow.

#### 1.5 Data-rate limitation

Limits on readout data rates are imposed by the G-Links between the trigger modules and RODs, and by the S-Links between the RODs and the ROS. It is also desirable to reduce the volume of data read out to DAQ in order to minimise the mass storage required for ATLAS events.

The number of G-Links handling DAQ data is kept to one per trigger module in order to minimise the power consumption per module, the number of RODs, and the system cost. (The number of RoI G-Links never needs to be more than one per module.) Once the full DAQ data rate can be handled by one G-Link per module, further data reduction can be

ROD Specification : File ROD-spec-version1\_1.doc Page 11 of 118

carried out by the RODs. The amount of data read out from each trigger module can be changed only by varying the number of timeslices of DAQ data that are read out, controlled by registers on the trigger modules. All modules of the same type should normally be set to read out the same number of timeslices. Except for the PPMs, the number of timeslices to be read out from a particular type of module is the same for all the different classes of data read out from a module. The number of timeslices of the two types of PPM data can be separately controlled, as the PPM cannot read out five timeslices of both FADC and LUT data at the full L1A rate of 100 kHz. At the maximum 100 kHz L1A rate, up to a total of eight timeslices (e.g. 5 FADC and 3 LUT) can be read. For most modules, more data can be read out at lower L1A rates.

Several tools are available to keep data rates within acceptable limits. Firstly, the number of timeslices read out from the trigger modules can be controlled. Secondly, the ROD can reduce the number of timeslices of each type of data independently. This may include entirely eliminating intermediate data that are not needed, especially when nominally equal to other data, e.g. at the two ends of data links in the trigger. Thirdly, data containing a large number of zeroes can be reduced in volume without loss of information by zero suppression. Finally, where some data values are much more frequent than others (e.g. in FADC data), loss-less data compression can be used to reduce data volume.

# 1.6 Organisation of ROD Modules

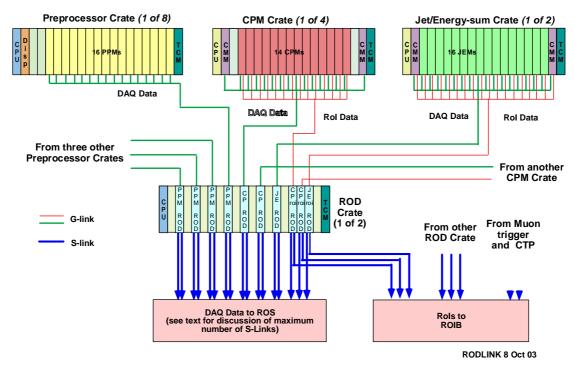

The four Cluster Processor crates each provide trigger signals covering one  $\phi$ -quadrant of the ATLAS detector, while the two Jet/Energy-Sum Processor crates each cover two  $\phi$ -quadrants. The eight Preprocessor crates are organised according to the topology of the different calorimeters. Twenty RODs are needed for the complete calorimeter trigger, enough to require two VME crates. Each ROD collects data from all the modules in one subsystem crate, so it is possible to carry most of the  $\phi$ -quadrant architecture into the two ROD crates, allowing the single-board computers in those crates each to access all the information from two quadrants (see Figure 3). In both ROD crates, this layout provides spare slots adjacent to DAQ RODs, and one empty slot adjacent to RoI RODs, so that expansion of the number of RODs is possible without completely reworking the connection database or adding another ROD crate.

In common with other trigger modules, the RODs determine their function by reading the geographical address of their VME slot, although this mechanism can be overridden for testing. Details of geographical addresses and functions are given in section 3.8.

Each ROD can drive up to four output S-Links, depending on its position in the system. The total number of RODs and S-Links is given in Table 1. G-Link and S-Link cabling details are defined in [10].

| Subsystem    | No of RODs | Links per ROD |         | Total L | inks    |

|--------------|------------|---------------|---------|---------|---------|

|              |            | to DAQ        | to RoIB | to DAQ  | to RoIB |

| Preprocessor | 8          | 4             | 0       | 32      | 0       |

| CP DAQ       | 4          | 2             | 0       | 8       | 0       |

| CP RoI       | 4          | 1             | 1       | 4       | 4       |

| JEP DAQ      | 2          | 4             | 0       | 8       | 0       |

| JEP RoI      | 2          | 1             | 1       | 2       | 2       |

| Totals       | 20         |               |         | 54      | 6       |

Table 1: Numbers of RODs and S-Links

Figure 3: Organisation of ROD input links and crates, showing one of two ROD crates.

# 2 Technical Aspects of the ROD Module

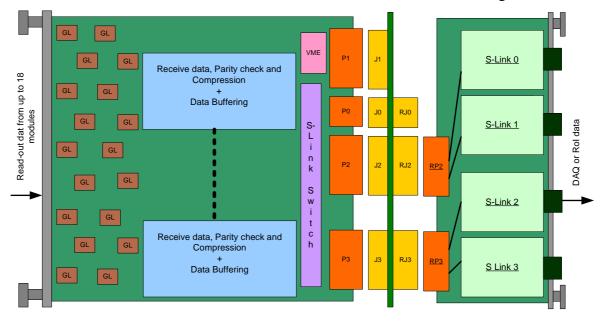

The ROD module is a VME64x [11] slave conforming to IEEE1101.10 [12], 9U x 400 mm form factor with on-board G-Link devices interfacing to the processing modules (PPMs, CPMs, JEMs and CMMs). The interface to the ROS and RoIB is via S-link cards hosted on a VME rear transition module similar to the CERN S2VME64x, as shown in Figure 4.

Figure 4: ROD module with S-Link rear transition module

ROD Specification : File ROD-spec-version1\_1.doc

RodOverview 14Oct06.vsd

# 2.1 Functional Requirements

The purpose of the ROD module is to collect data from the Preprocessor Modules (DAQ), Cluster Processor Modules (DAQ and RoI), Jet/Energy Modules (DAQ and RoI), and Common Merger Modules (DAQ and RoI), and send the formatted data on to the ROS and to RoIB. The ROD module provides the following functionality:

- a) Receive data sent optically at 18 x 800 Mbit/s using 18 G-Link Rx chips on board in 16- or 20-bit frame mode, with handling of link loss and transmission abnormalities.

- b) Compare the transmitted bunch numbers with the on-board TTCrx generated numbers. If the two do not match, set an error flag in the readout data.

- c) Perform parity check on the incoming G-Link data.

- d) Perform compression or zero suppression on data from each channel as required.

- e) Provide options to select reduced numbers of timeslices from different sections of source modules.

- f) Provide an option to bypass all formatting and compression logic and write a copy of the raw incoming data as output.

- g) Write formatted data (see section 5 for data formats) to the FIFO buffers (internal to the FPGAs)

- h) Receive TTC signals including clock, short broadcasts (BCR, ECR, and user bits), event number and event type, and construct event headers.

- i) Select data to be transferred to the ROS, on the basis of 'trigger type' received from the TTC.

- j) Transfer the data from header and FIFO buffers, followed by an event trailer, as ATLAS standard event fragments, to a rear transition module housing four S-Links.

- k) Flag G-Link data frames received with parity and link errors

- 1) Provide separate event buffers to spy on the data sent to S-links, with an option to selecting events according to event type.

- m) Provide access to the spy event buffers from the crate single-board computer via VME

- n) Provide a BUSY signal to the Central Trigger Processor via ROD Busy Modules [13].

- o) Process complete events at up to 100 KHz sustained rate.

- p) For RoI data only, terminate RoI data transfer if the number of RoIs is greater than a programmable limit, discarding any additional RoIs, and flag in status words.

- q) Support CANBus board temperature and voltage monitoring.

The ROD module processes many different data formats, and should be adaptable to the different requirements by loading the appropriate firmware under computer control.

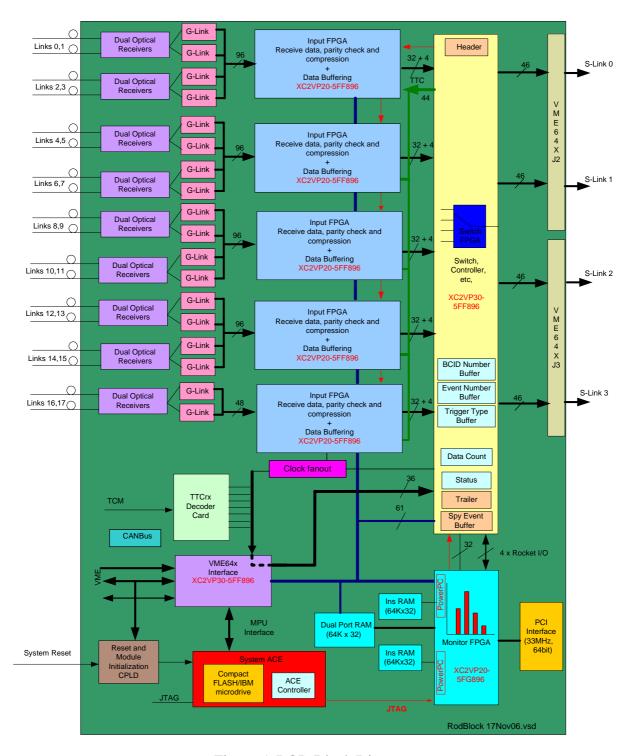

Figure 5 shows a block diagram (not the planned implementation) of the module.

Figure 5: ROD Block Diagram

# 2.2 Readout Process

There are six types of DAQ input G-Link data and four of RoI input, as shown in Table 2 below. The data format for each source is described in the corresponding section. A neutral format is also provided to allow generic processing of data from any source for diagnostic use. Each data source has a corresponding firmware type. For completeness, the table also lists the other firmware types used in the ROD module. These are described later.

| Firmware Type | Data Processing Type             | Section |

|---------------|----------------------------------|---------|

| 0             | Neutral – all sources            | 5.3     |

| 1             | Pre-processor non-compressed DAQ | 5.4     |

| 16            | Pre-processor compressed DAQ     | 5.4     |

| 2             | CPM DAQ                          | 5.5     |

| 3             | JEM DAQ                          | 5.6     |

| 4             | CMM-CP DAQ                       | 5.7     |

| 5             | CMM-Jet DAQ                      | 5.8     |

| 6             | CMM-Energy DAQ                   | 5.9     |

| 7             | CPM RoI                          | 5.11    |

| 8             | JEM RoI                          | 5.12    |

| 9             | CMM-Jet-E <sub>T</sub> RoI       | 5.13    |

| 10            | CMM-Energy RoI                   | 5.14    |

|               |                                  |         |

| 11            | Common                           |         |

| 12            | CPLD                             |         |

| 13            | VME FPGA                         |         |

| 14            | Switch FPGA                      |         |

| 15            | Monitor FPGA                     |         |

Table 2: ROD data sources and firmware types

#### 2.2.1 DAQ readout (slice) data

Transfer of data from G-Links to S-Links involves both the Input and the Switch FPGAs.

G-Link receivers (one G-Link per source module) are attached to the Input FPGAs, four to FPGAs 0-3, and two to FPGA 4, as shown in Figure 5. Each Input FPGA monitors the DAV\* signals from its G-Links, and starts receiving data when DAV\* goes active. The data are parity checked, zero-suppressed or compressed, formatted, and then stored in FIFO buffers to await readout. The amount of data received from each link is checked against the slice register.

When the Switch FPGA detects that all the Input FPGAs have completed processing for an event, it retrieves the event number and the Bunch-Crossing number from FIFOs, and places them in the header buffer FIFOs (one for each active S-Link) and then transfers the headers to the S-Links, followed by event data from the Input FPGA FIFOs, then followed by an event trailer. The number of S-links and the data routing to the appropriate S-Link depends on the volume of data and type of data as described in section 2.3.

The Switch FPGA also copies a selection of the data into the spy buffers. These data may subsequently be copied to the Monitor FPGA for analysis and/or transfer via the VME interface to a single board computer. In some cases (e.g. test run), event data may not be transferred out on the S-link, but it is still required that data are written to the spy buffers.

When the Level-1 Accept (L1A) signal arrives, the Switch FPGA inserts the event number (ROD L1ID, counted in the ROD - see 2.2.9) into its event number FIFO, and the Bunch-Crossing number (ROD\_BC, generated by the TTCrx) into its BC FIFO. These data are needed to build the S-Link header.

The Input FPGA puts another copy of ROD\_BC into its BC FIFO, which it uses to check the Bunch-Crossing number from the G-Link data. If there is a mismatch, a flag is set in the

ROD Specification: File ROD-spec-version1 1.doc Page 16 of 118 appropriate S-Link trailer and the lower six bits of the G-Link source Bunch-Crossing number are copied into the payload sub-status word. This condition should not occur if the system is in-step and operating correctly. On the first mismatch, and providing there were no parity errors, the controller records both Bunch-Crossing numbers in a register, together with the number of the G-Link involved, and sets a warning bit in the module status register. This information assists with problem diagnosis.

All the information needed to populate the main S-Link header comes from ROD registers. The source module identifiers needed to populate the sub-headers are assembled in the Input FPGAs from the SourceID registers. No crate or module number information is carried by the G-Links. The G-Link numbers for this calculation are listed in Table 6.

# 2.2.2 Single- and Multiple-timeslice data

All modules except the Preprocessor build the G-Link data frame by collecting data samples from their sequential processing stages, timed so that the data all relate to the same bunch crossing number. This tracks the time-evolution of the data through the algorithm – hence the term "timeslice". All modules can collect a programmable number of consecutive timeslices in response to each L1A, these data being sent as a continuous G-Link transaction, with DAV\* de-asserted only after the last timeslice of each L1A. The ROD should be configured by software to expect the same number and should normally expect all modules of the same type to send the same number of timeslices.

Except for the Preprocessor, the number of timeslices collected from different parts of a processing module pipeline must be identical to keep the G-Link formats simple. However, the ROD is able to select a reduced number of timeslices for onward processing into S-Link data. Data so eliminated is used only to complete longitudinal G-Link parity checking, and thereafter all bits concerned are ignored, including any error indicators. This capacity is described in section 2.5.

In the case of the Preprocessor, the number of FADC and PPM\_LUT timeslices may be varied independently using a control register within the PPM ASIC, up to a maximum of seven timeslices of LUT data and 127 of FADC data. The ROD normally expects no more than 31 timeslices in total (a header format restriction). It may be possible for time-isolated events to contain more data for test purposes, depending on available FIFO capability.

The control logic checking the Bunch-Crossing number arriving in the G-Link data stream expects all timeslices to carry the same bunch-crossing number, that of the L1A.

#### 2.2.3 Format of S-Link Event Fragments

Each S-Link packet is built from four components, described in section 3.6. These are the ATLAS-standard ROD header, a data payload, a status block, and an ATLAS-standard ROD trailer.

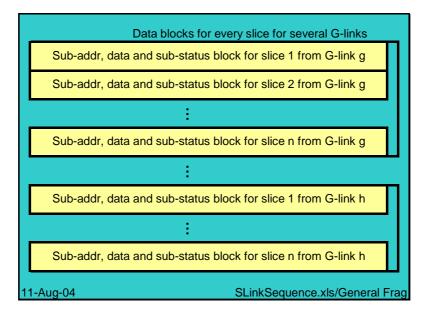

The payload from each source module is constructed in an Input FPGA. It consists of a sequence of data blocks (each comprising sub-address, data and sub-status) for each active G-Link in turn (numbered g to h in the following figures). Within each G-Link data block, the data format depends on the data source. S-Link data from CPMs, JEMs and CMMs consist of a sequence a sub-blocks, one for each timeslice. This structure is illustrated in Figure 6.

ROD Specification: File ROD-spec-version1 1.doc Page 17 of 118

Figure 6: Overall structure of event fragment payload (CPM, JEM, and CMM data)

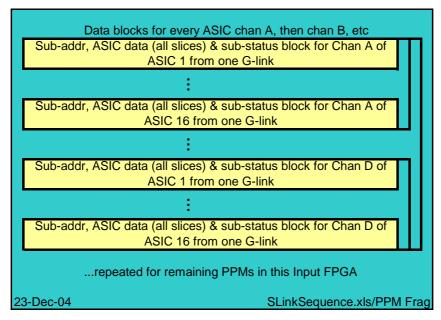

Data from the Preprocessor reflect the readout from the Preprocessor ASIC, and contain a sub-block for each channel (A-D) of each ASIC (0-15) per PPM. Each S-Link contains the data from an integral number of G-Links –usually four G-Links per S-Link. On each of the S-Links, the overall S-Link packet is as shown in Figure 7.

Figure 7: Overall structure of event fragment payload (PPM data)

The first word of each sub-block is a sub-address word. This includes a version number of the sub-block format, the slice number, and the source module crate and slot numbers. After the data part of the sub-block comes a sub-status word whose content includes error bits relating to the data of the sub-block. Errors are indicated by non-zero bits, so the sub-status may be zero-suppressed if no error bits are set.

The firmware responsible for each enabled G-Link always produces a sub-address word, even if all other data are eliminated from the sub-block by zero-suppression or compression. The sub-address is also produced if there is a timeout for a G-Link. Only if a G-Link is disabled by ROD control registers are no data or sub-status words produced.

ROD Specification: File ROD-spec-version1 1.doc Page 18 of 118 To maintain the maximum throughput, the ROD should treat the active S-Links as separate channels. Event headers, data payload and event trailers should be transferred independently and concurrently to all active S-Links. Presence of Link Full Flag (LFF, i.e. Xoff) on one link does not prevent data transmission on other active links. There is an exception for RoI and DAQ-copy (diagnostic) modes, in which LFF on either the RoIB or ROS S-Links should suspend transmission on both. This is necessary since the two S-Links carry copies of the same data payload.

Memory-mapped VME access to the data buffers is needed for testing. Valid data lies between the read and write pointers, which should be read to ascertain the location and length of valid data.

#### 2.2.4 G-Link Timeout

Cable and module faults may cause G-Link data not to arrive. A timeout mechanism is provided to identify and recover from such faults by generating a short status block for missing G-Link inputs, so that the rest of the readout can proceed unchanged. The Event Counter Reset signal (see section 2.2.9) ensures that the ROD recovers from the effect of temporary glitches.

In normal operation, the Switch FPGA waits for all Input FPGAs to signal that they have a formatted event sub-block available. Since the Input FPGA readout and formatting process is pipelined, formatted data from all active G-Links should be available within about 10µs after an L1A if the links were previously idle. Data transfer out of the Input FPGAs starts when they are all ready.

The timeout logic operates independently for each S-Link, using a separate timeout counter for each. The first data-ready signal from an Input FPGA routed to a given S-Link starts the timeout counter. After a programmable interval has elapsed (e.g. 11 µs), other inputs routed to the S-Link are timed-out. Data are again transferred out of the Input FPGAs, with those that have timed out providing a timeout indicator block. The timeout condition is indicated via the sub-status word and copied by the Switch FPGA into the event trailer.

Once the timeout mechanism has been triggered, timeout indicator blocks are produced for all failing Input FPGA channels, even if formatted data arrive late and are ready by the time they are needed for readout. The late data cannot be distinguished (by the Input FPGA) from the following event.

The ROD should therefore be robust against removal and replacement of the G-Link input during normal operation.

# 2.2.5 G-Link DAV Gap

The ROD uses the G-Link DAV\* signal to frame data from each event. Input data formatting in the ROD is controlled by a state machine, which requires a small number of extra clock cycles to complete after the last incoming data are received. G-Link source modules must hold the DAV\* signal inactive for at least this period, referred to as the "DAV Gap", even if another event is ready for transmission. The duration of the gap depends on the type of firmware in use in the ROD, so should be coded as a programmable parameter in the upstream readout firmware. The DAV Gap length is independent of the number of timeslices being read out.

The required value is at present 1 for all firmware variants except Neutral, which requires a DAV GAP of 3 ticks.

ROD Specification : File ROD-spec-version1\_1.doc Page 19 of 118

# 2.2.6 Trigger Type Timeout

There is a time delay between receipt of the L1A and of the trigger type information. The minimum time is  $1.05~\mu s$  and the maximum unknown. If the trigger type does not arrive within a pre-defined time (programmable register) the event is built with the trigger type information set to 0xFF, and a timeout indicated in the status register.

# 2.2.7 Handling S-Link Link Full

The Switch FPGA monitors the Link Full Flag (LFF) signal from all active S-Links, and pauses any data transfers within two clock cycles whenever the S-Link becomes temporarily full, as required by the S-Link specification. LFF may occur at any time, independently on any combination of the active S-Links, and the duration may be any period from 1 clock cycle upwards. Since the LFF signal prevents data transfer out of the ROD module, the incoming data may overflow the Input FPGA buffers. To prevent this, the ROD must assert "BUSY", asking the CTP to stop sending triggers, before the buffers get full.

Note that LFF is often referred to within ATLAS as Xoff. The ROD has the capability to generate an internal LFF signal under software control to pause traffic on any S-Link.

# 2.2.8 Handling ROD Busy

The ROD continuously compares the depth of data stored in each Input FPGA to a programmable threshold. The ROD sets the BUSY bit in the status register and asserts the BUSY front-panel output whenever the threshold is exceeded, and removes these signals when all buffer levels fall to the threshold or below. Empty buffers never cause BUSY even if the threshold is zero, and BUSY is never asserted if the threshold is set equal to the physical buffer depth.

The BUSY signal is passed to the CTP via the BUSY modules. Several events may be awaiting readout, and more may be triggered before the BUSY takes effect. The threshold should be set to ensure that enough buffer space is available in the RODs to accommodate the maximum possible number of events, estimated to be about eight, of the maximum expected size.

If, despite the BUSY logic, the ROD buffers do overflow, data are lost. In this case the ROD sends whatever data are available, but always provides at least an event header and trailer with appropriate status bits set.

### 2.2.9 Event Counter and Event Counter Reset

The CTP will transmit Event Counter Reset (ECR) signals at a programmable rate of around 1 Hz, depending on the LHC luminosity. ECR is counted in an eight-bit register which is copied into the ECRID field in the S-Link event header.

The ECR mechanism was designed long after the TTCrx ASIC design was complete, so the ASIC does not clear its internal Level-1 ID (event counter) on receipt of ECR. For this reason, the ROD must maintain its own 24-bit L1\_ID counter, which should be incremented on receipt of an L1A and cleared on receipt of ECR [14]. The value of this counter should be used to provide the ROD\_L1ID field in the ROD S-Link header.

ECR is also used to ensure that any unused event data left in the ROD following a timeout are removed cleanly. No L1A occurs during two dead-time intervals of around 1 ms each, generated in the CTP, immediately preceding and following an ECR. The limiting case is that eight events are triggered immediately prior to the start of ECR dead-time. The longest G-

ROD Specification : File ROD-spec-version1\_1.doc Page 20 of 118

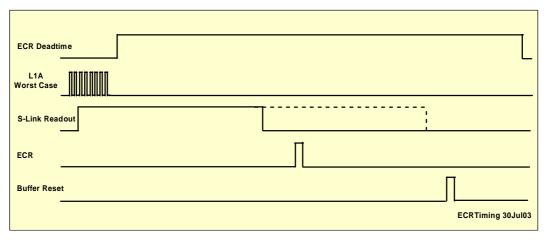

Link readout is the 84-bit sequence per timeslice from the CPM. Eight such events of five timeslices each take just under 84 us to send to the ROD. The 1 ms is also long enough to transmit 100 events to the ROS or RoIB, and ROD BUSY is used to ensure that the data volume stored in the ROD never reaches this level. At a programmable interval (less than 1 ms) after the ECR, the ROD generates Buffer Reset, which clears the pending L1A counter and purges all Input FPGA buffers and the FIFOs holding Level-1 Event Type, BCN, and Orbit. An indicative timing sequence is shown in Figure 8 below.

Figure 8: Timing sequence of signals related to Event Counter Reset

#### 2.2.10 RoI Data

The principle of data transfer for the RoIs is as above, except for the bit field definitions and the requirement to limit the number of RoIs transmitted to the RoIB from each ROD. If more than a predetermined number of RoIs are received in any one ROD from the CPMs, JEMs, or CMMs, that ROD terminates the RoI transmission and indicates this via a bit in one of the status words.

Sorting the RoIs prior to discarding any beyond the transmission limit, as suggested in [15], is a complex operation and is not implemented.

### 2.3 Data Transfer Rates in the ROD

The data volume into and out of the RODs depends on several parameters, including the type of module, the number of timeslices being read out, the L1A rate, and the effectiveness of the zero suppression or compression algorithm (discussed in section 2.5). Compression efficiency depends strongly on the occupancy of calorimeter cells and hence the LHC luminosity and background conditions.

#### 2.3.1 G-Link input data rates

Table 3 shows some parameters for the G-Links from different source modules. The G-Link frame lengths and number of active bits (excluding padding zero bits) are given for one timeslice. For the PPM, the figures are for one timeslice of LUT data and five of FADC data, a combination likely to be used but requiring compression at full trigger rate. Also shown are the resulting incoming data rates in Mbytes/sec when running the trigger at 100 kHz. The final column shows the overall input rate for a ROD servicing a full crate of each type, including system-summing CMMs. Data rates for non-system-summing crates are slightly lower.

| ROD Type | Source<br>Module | G-Link<br>frame length<br>(bits) | G-Link<br>active bits<br>per link and<br>per frame | Data rates at 100 kHz L1A<br>and 3 (DAQ), 5+1 (PPM<br>DAQ), or 1 (RoI) timeslices<br>(MB/s) |           |

|----------|------------------|----------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|-----------|

|          |                  |                                  |                                                    | per G-Link                                                                                  | ROD Total |

| PPM DAQ  | PPM              | 276                              | 4412                                               | 55                                                                                          | 882       |

|          | CPM              | 84                               | 1680                                               | 63                                                                                          | 882       |

| CP DAQ   | CMM              | 35                               | 505                                                | 19                                                                                          | 38        |

|          | Total            |                                  |                                                    |                                                                                             | 920       |

|          | JEM              | 67                               | 1046                                               | 39                                                                                          | 628       |

| JEP DAQ  | Jet-CMM          | 35                               | 561                                                | 21                                                                                          | 21        |

| JEF DAQ  | En-CMM           | 35                               | 590                                                | 22                                                                                          | 22        |

|          | Total            |                                  |                                                    |                                                                                             | 671       |

| CP RoI   | CPM              | 22                               | 348                                                | 4                                                                                           | 61        |

|          | JEM              | 45                               | 193                                                | 2                                                                                           | 39        |

| JEP RoI  | Jet-CMM          | 35                               | 16                                                 | 0.2                                                                                         | 0.2       |

| JEL KOI  | En-CMM           | 35                               | 60                                                 | 0.8                                                                                         | 0.8       |

|          | Total            |                                  |                                                    |                                                                                             | 40        |

Table 3: G-Link data rates into RODs

These figures are computed directly from the data formats shown in section 5 (in fact the diagrams are EXCEL drawings produced by macros, which also compute the data lengths). For example, the CPM has a frame length of 84 bits. All 20 bits are used for each timeslice, making a total of 1680 bits. The 20 longitudinal parity bits are not repeated in a three-timeslice frame, so three timeslices require 3\*1680 - 2\*20 = 5000 bits = 625 bytes. At 100 kHz of L1A, this amounts to 62.5 Mbytes/sec per G-Link (excluding ROD headers and trailers). For 14 active G-Links this total incoming data rate is 875 Mbytes/sec.

An example for the JEM shows the effect of unused bits. The JEM has a frame length of 67 bits, but in the overall frame 22 bits are unused on pin D14 and four on D15. A frame thus provides 67\*16-26=1046 bits. The calculation is completed assuming 16 active links.

# 2.3.2 Maximum Trigger Rates

ATLAS detectors, including the trigger, must be capable of readout at 75 kHz, and must be capable of upgrade to 100 kHz. In the calorimeter trigger, the CPM readout over G-Link requires 84 clock periods to read out each timeslice of data. To reach 100 kHz, the number of timeslices must be restricted to four or less (4 \* 84 \* 25 ns = 8.4  $\mu$ s). A possible reduction in the CPM format would give a data length under 80 clock cycles. For the PPM, the ASIC can be configured to read out less than five timeslices, but the G-Link packet length of 276 clock ticks is already fast enough(276 \* 25 ns = 6.9  $\mu$ s). The JEM and CMM readout lengths, 67 and 35 per slice, respectively, are both short enough to allow 100 kHz readout of five timeslices.

A DAV gap is not included in the above calculations. If set to 1 tick as required for all except neutral format, it consumes about 0.2% of the available readout time at 100 kHz.

ROD Specification : File ROD-spec-version1\_1.doc Page 22 of 118

# 2.3.3 S-Link output data rates

Converting the G-Link data into 32-bit S-Link words causes the data to expand, due to the addition of addresses and internal headers. Zero suppression and data compression are needed to fit the data plus event headers and trailers into the available S-Link output bandwidth. The degree of data reduction depends on the detector occupancy, and the output data volume may be managed by choice of the number of timeslices read out from different stages of the various modules.

Table 4 shows the estimated data rates and the occupancy of the S-links when the trigger tower occupancy is 5% of uncorrelated hits, the L1A rate is 100 kHz, and 3 timeslices (PPM 5+1 slices) are being read from all planned inputs per ROD, without discarding any intermediate data. It is pessimistically assumed that about 10 percent of RoIs survive after zero suppression. The data volumes scale linearly with L1A rates if no other conditions change. The calculation does not include the two S-Link control words, ATLAS-standard ROD header (9 longwords), user header (1 longword), status block (2 longwords), and trailer (4 longwords), which total 72 bytes per link per event, or 5.4 Mbytes per link at 75 kHz. This is 3.4% of the S-Link bandwidth.

| ROD Type | Source  | Uncompressed | Compression | Compressed | S-Links/ | S-link    |

|----------|---------|--------------|-------------|------------|----------|-----------|

|          | Module  | O/P (MB/s)   | Factor      | O/P (MB/s) | ROD      | Occupancy |

| PPM      | PPM     | 986          | 2           | 493        | 4        | 77%       |

| DAQ      |         |              |             |            |          |           |

| CP DAQ   | CPM     | 1395         | 9           | 152        |          |           |

|          | CMM     | 65           | 3           | 22         |          |           |

|          | Total   | 1459         |             | 174        | 2        | 54%       |

| JEP DAQ  | JEM     | 922          | 2.8         | 310        |          |           |

|          | Jet-CMM | 25           | 7           | 4          |          |           |

|          | En-CMM  | 25           | 1           | 25         |          |           |

|          | Total   | 972          |             | 358        | 4        | 56%       |

| CP RoI   | CPM     | 896          | 20          | 45         | 1+1, to  | 28%       |

|          |         |              |             |            | DAQ &    |           |

|          |         |              |             |            | RoIB     |           |

| JEP RoI  | JEM     | 58           | 2.9         | 20         |          |           |

|          | CMM-J   | 25           | 7           | 4          |          |           |

|          | CMM-E   | 25           | 1           | 25         |          |           |

|          | Total   | 108          |             | 48         | 1+1, to  | 30%       |

|          |         |              |             |            | DAQ &    |           |

|          |         |              |             |            | RoIB     |           |

Table 4: Estimated S-Link Data Rates from each ROD

# 2.4 S-Link Mapping

The diagrams below show the connectivity between G-Link buffers and S-Links to achieve the data rates in Table 4. The configuration of the switching should be independent of the G-Link input firmware, so that the number of output S-Links in use on any ROD can be set as the L1A rate and data volume require. S-Link port 2 has a logic analyser header, and is included in all mapping arrangements.

ROD Specification : File ROD-spec-version1\_1.doc Page 23 of 118

# 2.4.1 RoI Data from CPM, JEM, and CMMs

Two copies of RoI S-Link output data are required, one destined for the RoIB and one for the ROS. These data differ only in the S-Link identifier value used in the header (see 3.6.2). Data are routed as shown in Figure 9. This connectivity may also be used for DAQ diagnostics at low data rates, in which case the duplicated output to S-Link 2 is not required.

G-Link inputs for RoI data from the CP and JEP subsystems are assigned as shown in Table 5. For testing purposes, it is necessary to operate when some of the source modules are unavailable. In this case, the corresponding G-Link inputs should be disabled in the G-Link disable register.

Figure 9: RoI S-Link mapping, showing active (solid) and unused (dashed) data paths.

Note that only one of the two JEP RoI RODs (that receiving data from the CMM system crate) has RoI input from CMMs.

ROD Specification: File ROD-spec-version1\_1.doc

| Subsystem | G-Link | Use                                                        |

|-----------|--------|------------------------------------------------------------|

| CP (RoI)  | 0      | Disabled by software                                       |

|           | 1-14   | CPM RoI                                                    |

|           | 15-17  | Disabled by software                                       |

|           |        |                                                            |

| JEP (RoI) | 0-15   | JEM RoI                                                    |

|           | 16     | CMM Energy (left) RoI (from JEP system-summing crate only) |

|           | 17     | CMM Jet (right) RoI (from JEP system-summing crate only)   |

Table 5: G-Link use for RoI Data

# 2.4.2 DAQ Data from Preprocessor, CP and JEP

Figure 10 shows the connectivity between the ROD and the S-Links. Four S-Links are required to carry the data volume generated in the PPMs and the JEMs when running at the maximum L1A rate, while only two S-Links (numbers 0 and 2) are needed for the CPMs. At lower rates, data from PPMs and JEMs should also be presented on S-Links 0 and 2. At the lowest rates, using a single S-Link, as in Figure 9, is adequate.

Figure 10: DAQ data S-Link mapping for JEP crates

G-Link inputs for DAQ data from the Preprocessor, CP and JEP subsystems are assigned as shown in Table 6. Each ROD handles all the DAQ data from a complete Preprocessor, CP or JEP processing crate.

Two RODs reading data from Preprocessor crates receive input from only 14 PPMs, which are located in slots 6-12 and 14-20. The G-Link inputs are assigned to mirror the occupied PPM crate slots.

ROD Specification : File ROD-spec-version1\_1.doc Page 25 of 118

| Subsystem | G-Link | Use                     |

|-----------|--------|-------------------------|

| PPM (DAQ) | 0-15   | PPM DAQ                 |

|           | 16-17  | Unused                  |

| CP (DAQ)  | 0      | Unused                  |

|           | 1-14   | CPM DAQ                 |

|           | 15     | Unused                  |

|           | 16     | CMM e.m/tau. (left) DAQ |

|           | 17     | CMM e.m (right) DAQ     |

| JEP (DAQ) | 0-15   | JEM DAQ                 |

|           | 16     | CMM Energy (left) DAQ   |

|           | 17     | CMM Jet (right) DAQ     |

Table 6: G-Link use for DAQ data

# 2.5 Zero suppression and compression

Various forms of data reduction are needed to reduce the size of the S-Link packets going to the ROS or RoIB. The S-Link output data are used downstream to check the trigger performance, so the data reduction process must be loss-less, i.e. it must be possible to recreate the ROD input accurately from compressed readout data. There are four basic tools for data reduction:

- The number of timeslices of data read out from the trigger modules is controlled on the modules themselves.

- The number of timeslices of data can be reduced further in the ROD. This includes the possibility of eliminating some data altogether (e.g. from the two ends of data links) by setting the number of timeslices to zero.

- Zero suppression see section 2.5.1.

- Compression see section 2.5.2.

The last three operations are carried out in the ROD Input FPGAs.

A further requirement is that suppression and compression must handle the full data rate into the ROD at the maximum specified L1A rate of 100 kHz and at the incoming G-Link clock frequency of 40 MHz. All such suppression and compression are therefore done in pipelined firmware. The CPUs in the ROD FPGAs are not used for this purpose.

For diagnostic use, it must be possible to process data without suppression or compression. This capability is provided by the "neutral" data format. However, a limit on the maximum size of an S-Link packet is imposed by both the ROS and RoIB, so uncompressed data are unlikely to be acceptable in normal running.

ROD Specification: File ROD-spec-version1 1.doc

#### 2.5.1 Zero suppression

The G-Link input data from some modules will contain many zero values. Examples include the RoI data from the CPMs and the JEMs, and DAQ data from the CPMs, JEMs, CMMs, and PPMs (LUTs).

The ROD is capable of zero-suppressing such data. To do this, incoming data are discarded if all data, error, and saturation bits are zero, and the surviving data are then labelled with channel, module, and crate addresses. Details of the criteria for zero suppression are provided with each data format in section 5.

#### 2.5.2 **Compression**

Data from the Preprocessor consists of raw FADC samples and one or more PPM\_LUT values per channel. For much of FADC readout, the data have small non-zero values close to the FADC pedestal, and zero suppression is not effective. Lossless data compression is needed, and three output formats are specified:

- an uncompressed format, in which the output data contain the full data value for each input datum. This format is used only for diagnostics or when the numbers of timeslices to be read out do not match the compressed (or super-compressed) format. This format is as close as possible to the input data format.

- a compressed format, in which the PPM\_LUT output and FADC data are packed into short bit fields, with longer bit fields available to encode larger values. This format, intended to handle only 1 LUT sample and five FADC samples, is described in [16].

- a super-compressed format, similar to the compressed format, except that data are omitted for those Preprocessor channels in which the PPM LUT result is zero and the FADC samples are all below a programmable (per G-Link) threshold. This format is loss-less only for those Preprocessor channels with a non-zero PPM\_LUT output or an energetic FADC sample.

Details are given with the data formats in section 5.

# 2.6 Data Replay Mode

The ROD provides a data replay mode for testing the switch and monitoring functions, and to provide test S-Link data for the ROS and RoIB. Details are included in section 3.13.

Data to be replayed must be loaded by software into the FIFOs in the Input FPGA, together with the details of the event lengths it contains. When in replay mode, the Input FPGA ignores the G-Links, and instead sends data directly from the FIFOs associated with enabled channels. In replay mode, the data read from the FIFOs is also recycled back to the FIFO input so that an indefinite number of events may be sent.

Replay data readout is initiated, as in normal ROD operation, by a L1A, either arriving via the TTC or generated internally to the ROD by VME command to the pulse register. FIFOs should be cleared by software before terminating replay mode.

# 3 Functional blocks

This section describes the functional blocks shown in Figure 5.

# 3.1 Optical Inputs

The physical connections between the ROD module and the processor modules (PPM, CPM, JEM, and CMM) are via optical links operating at 960 Mbaud. The receivers are small form-factor commercial 1.25 Gigabit Ethernet compliant, optical dual receiver modules with LC type connectors (the M2R-25-4-1-TL from STRATOS Lightwave [17]). Nine of these modules fit on the ROD to interface to 18 links.

### 3.2 G-Link

The interface between the optical receivers and the FPGAs uses a commercial "G-Link" serial to parallel converter and clock recovery receiver chip HDMP1024 (Rx) from Agilent Technologies. This chip can receive 16-bit or 20-bit data. The corresponding parallel to serial converter on the processor modules (PPM, CPM, and CMM) is the transmitter chip HDMP1022 (Tx). The JEM uses the compatible HDMP1032 (Tx). The 18 HDMP1024 receiver chips on the ROD each connect to a single processor module via the optical receivers. Depending on the position within the system, not all 18 G-Links are required at all times.

The G-Link chips operate in "Simplex method 2", in which the receiver requires a synchronisation signal from the transmitter. The synchronisation signal is routinely sent during DAV gaps. The G-Link receiver does not require a local reference clock, although a 40 MHz crystal oscillator on board is provided to generate a clock source for testing when the TTC is not present. To prevent problems, selection of a TTC source is prohibited if the TTC is not present, or not ready.

Two G-Link input pins, DIV0 and DIV1, define the frequency range over which the G-Link can operate. DIV1 is pulled to ground on the PCB, while DIV0 is under control of the Input FPGA firmware. At present it is driven as the inverse of the mod20sel level, which is set by VME. This is due to the difference in frequency ranges in the 16- and 20-bit modes of the G-link.

VME-readable link loss and error counters must be provided for each G-Link.

# 3.3 Input FPGA