# ATLAS Level-1 Calorimeter Trigger Prototype Processor Backplane

**Project Specification (FDR)**

Version 1.1 Date: May 2, 2005

**Samuel Silverstein**

Stockholm University

## **Table of Contents**

| Table of Contents                                    |    |

|------------------------------------------------------|----|

| Document History                                     |    |

| 1 Introduction                                       | 4  |

| 1.1 Overview                                         | 4  |

| 1.2 Scope of this document                           | 4  |

| 1.3 Related projects                                 | 4  |

| 2 Functional requirements and implementation         | 4  |

| 2.1 Backplane dimensions and organisation            |    |

| 2.2 Printed circuit board                            |    |

| 2.3 Connectors                                       |    |

| 2.4 Backplane connections                            | 8  |

| 2.4.1 Serial link inputs                             |    |

| 2.4.2 Data fan-in/-out                               |    |

| 2.4.3 Real-time results merging                      |    |

| 2.4.4 Timing, trigger and control (TTC) distribution |    |

| 2.4.5 CAN bus                                        |    |

| 2.4.6 Reduced VME bus                                |    |

| 2.4.7 Geographic addressing                          |    |

| 2.4.8 Power distribution                             |    |

| 2.5 Line impedance                                   |    |

| 2.6 Mechanics                                        |    |

| 2.7 Grounding                                        |    |

| 2.8 Environmental Conditions                         |    |

| 2.9 Backplane-to-module pin assignments              |    |

| 2.9.1 CPU                                            |    |

| 2.9.2 CMM                                            |    |

| 2.9.3 CPM/JEM                                        |    |

| 2.9.4 TCM                                            |    |

| 2.9.5 CANbus connector                               |    |

| 2.10 Connector numbering and silkscreen              |    |

| 3 Prototype PB test results                          |    |

| 3.1 Connectivity                                     |    |

| 3.2 Impedance                                        | 14 |

| 3.3 Propagation delays                               | 14 |

| 3.4 Cross talk                                       | 15 |

| 3.4.1 Merger-Merger cross talk                       | 15 |

| 3.4.2 FIO-LVDS cross talk                            | 15 |

| 3.4.3 VME–Merger cross talk                          | 16 |

| 3.4.4 Full system tests                              | 16 |

| 3.5 TTC signal quality                               | 16 |

| 3.6 Power distribution                               | 17 |

| 3.7 Mechanics                                        | 17 |

| 3.8 Module keying                                    | 17 |

| 3.9 Repair and maintenance                           | 17 |

| 3.10 Errata                                          | 18 |

| 3.10.1 PCB errors                                    |    |

| 3.10.2 Mechanical issues                             | 18 |

| 4 Project management                                 |    |

| 4.1 Overview and deliverables                        | 19 |

| 4.2 Personnel                                        |    |

| 4.3 Design and verification                          |    |

| 4.4 Manufacturing                                    |    |

| 4.5 Pre-production testing                           |    |

| 4.6 Production testing                               |    |

| 4.7 Costs                                            |    |

| 5 Production and distribution                        |    |

| 6 Summary                                            |    |

| Glossary                                             |    |

| References                                           | 21 |

| Appendix A: CPU interface connector layout          | 22 |

|-----------------------------------------------------|----|

| Appendix B: CMM connector layout                    | 24 |

| Appendix C: CPM/JEM connector layout                |    |

| Appendix D: TCM interface connector layout          | 32 |

| Appendix E: Design checklist for manufacturer       |    |

| Appendix F: Bill of Materials                       |    |

| Appendix G: PCB Quote Sheet                         |    |

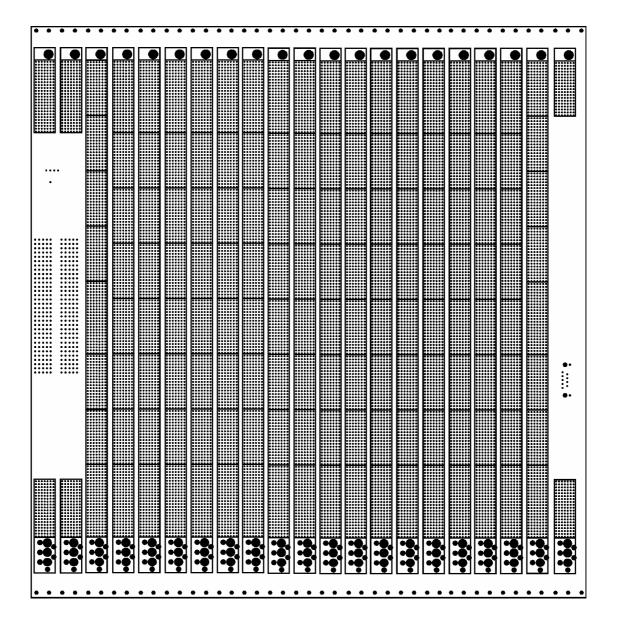

| Appendix H: Sketch of PB printed circuit board      | 38 |

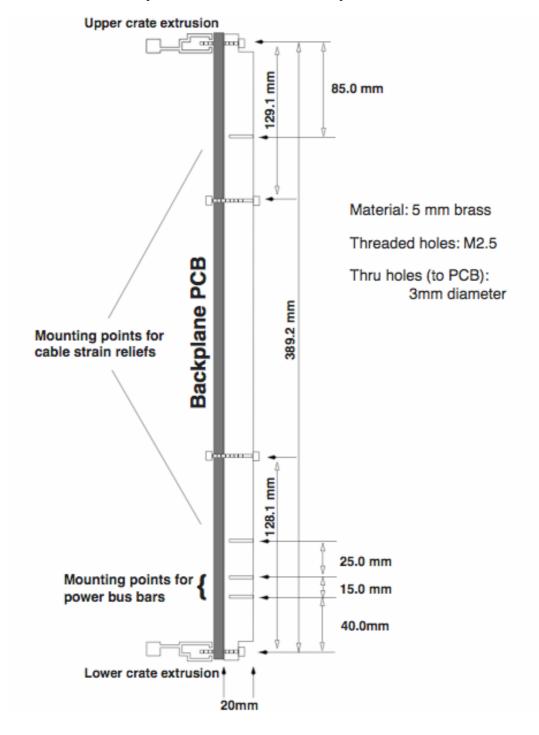

| Appendix I: Sketch of PB support hardware           | 39 |

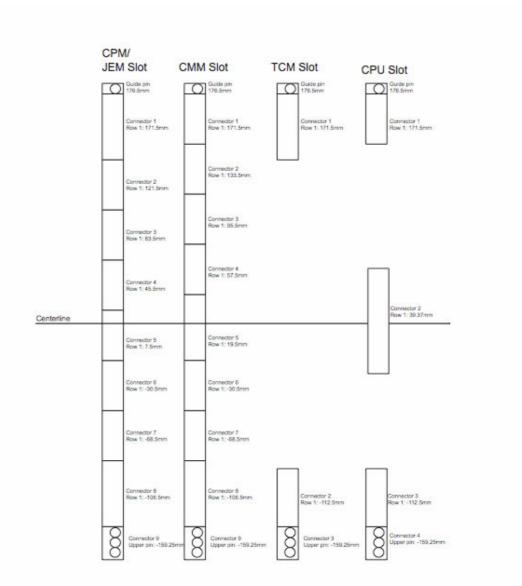

| Appendix J: Vertical positions of module connectors |    |

## **Document History**

| Version 0.1 | (November 8, 2004)  | Initial review and advance distribution to manufacturers                                                                                                                                                                                                                             |

|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version 0.2 | (November 21, 2004) | Addition of new test results from RAL<br>Clarification of differential impedances<br>Most initial corrections suggested by reviewers                                                                                                                                                 |

| Version 0.3 | (December 1, 2004)  | More corrections suggested by reviewers<br>Added CANbus pinout (2.9.5)<br>Connector numbering and silkscreen (2.10)<br>TTC signal quality (3.5)<br>Module keying (3.8)<br>Treatment of mixed LVDS/FIO cable headers (3.10.2)<br>Expanded test planning for production PB (4.4 - 4.6) |

| Version 1.0 | (April 10, 2005)    | Implemented changes recommended by FDR committee<br>Updated BOM and other manufacturer specifications                                                                                                                                                                                |

| Version 1.1 | (May 2, 2005)       | Added last-minute changes to specification before starting tender process                                                                                                                                                                                                            |

## **1** Introduction

This document has been produced for the final design review (FDR) of the ATLAS

Level-1 Calorimeter Trigger Processor Backplane and its respective mechanical hardware. It includes updated specifications based on prototype experiences, as well as test results from the prototype programme.

### 1.1 Overview

The Processor Backplane (PB) for the ATLAS Level-1 calorimeter trigger is used for both the Cluster Processor (CP) and the Jet/Energy Sum Processor (JEP) subsystems. Its functions include:

- Hosting 14 Cluster Processor modules (CPMs) or 16 Jet/Energy Modules (JEMs), two datamerging modules (Common Merger Modules, or CMMs), one Timing and Control Module (TCM) and at one or two local VME CPUs (CPU).

- Receiving serial cable links from the PreProcessor system (PPR) and feed their signals to the JEMs or CPMs in the crate.

- Providing point-to-point connections for data sharing between neighbouring CPMs or JEMs.

- Providing point-to-point connections from each processor module to both CMMs for real-time results merging.

- Distributing timing, trigger and control (TTC) signals from the TCM to all other modules.

- Provide a reduced-function VME-based bus to all modules in the crate (VME--).

- Host a differential CAN bus for slow control and monitoring of all modules.

- Provide extended geographical addressing system with unique identifiers for every module in the CP and JEP systems, for specifying VME, TTC, and CAN addresses for that board, and select position-dependent configuration options.

- Provide up to 25A of combined 5V and 3.3V power to each module.

### **1.2 Scope of this document**

The scope of this document is to describe the specification for the production Processor Backplane, including changes from the prototype design, and to review the results of the prototype test program. The appendices include documentation necessary for prospective backplane manufacturers to submit a bid during the tendering period.

The document is structured as follows: Section 2 describes the functional requirements of the Processor Backplane and how these are implemented. Section 3 describes the results for prototype backplane test program. Section 4 describes aspects of the management of the project, and Section 5 provides time scales for production and installation of the production backplane.

### 1.3 Related projects

The PB provides the primary interface between several other components of the Level-1 Calorimeter Trigger, which are being developed in parallel with this project. Existing documentation for these components can be found at <u>http://hepwww.rl.ac.uk/Atlas-L1/Modules/Modules.html</u>. The relevant modules and their latest document versions at the time of writing are:

| CPM | Version 1.03 (post PDR)            |

|-----|------------------------------------|

| JEM | Version 1.0.1 (PDR)                |

| TCM | Version 1.0 (PDR)                  |

| CMM | Version 1.5 (Module Specification) |

| VMM | Draft 1 (2002)                     |

These related components have been through, or will shortly undergo, reviews of their own, and the requirements for the PB are matched to the components of the CP and JEP systems.

## 2 Functional requirements and implementation

This section introduces the requirements on the functions of the Processor Backplane, and how they are implemented

### 2.1 Backplane dimensions and organisation

The Processor Backplane is installed in a modified CERN standard crate with 9U nominal height (400.05 mm) and 84 HP width (426.72 mm), conforming with IEEE 1101.10 specifications. The crate accepts up to 21 modules of 4HP width (20.02 mm) each, with a vertical height of 366.7 mm and a depth of 400mm. Each position is designed to service only one type of module. The organisation of modules in the processor crate is presented in Table 1.

| Position(s)    | Module Type                                                   |

|----------------|---------------------------------------------------------------|

| 1 and/or 2     | VME Controller (CPU), mounted in 9U VME Mount Module (VMM)    |

| 3              | Common Merger Module (CMM)                                    |

| 4-19 (or 5-18) | Jet Energy-Sum Module (JEM) or Cluster Processor Module (CPM) |

| 20             | Common Merger Module (CMM)                                    |

| 21             | Timing and Control Module (TCM)                               |

Table 1: Processor Backplane Organisation.

Position 1 is located at the left side of the crate, viewed from the front, while position 21 is at the right side. In this document, "left" and "right" refer to lower and higher position numbers, respectively. The "front" side of the backplane refers to the side facing the front panel of the rack, where the processor modules are connected.

The processor modules are arranged in order of increasing  $\eta$  with increasing position number. Each JEP crate hosts two contiguous groups of 8 JEMs corresponding to opposite quadrants in  $\phi$ . This arrangement is designed to expedite missing energy calculations in the merger modules by allowing direct subtraction of  $E_x$  and  $E_y$  values. In both JEP crates, the left-most group of 8 JEMs is assigned to a quadrant with smaller  $\phi$  than the right-most group.

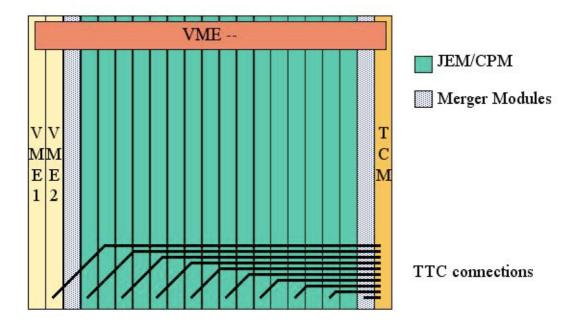

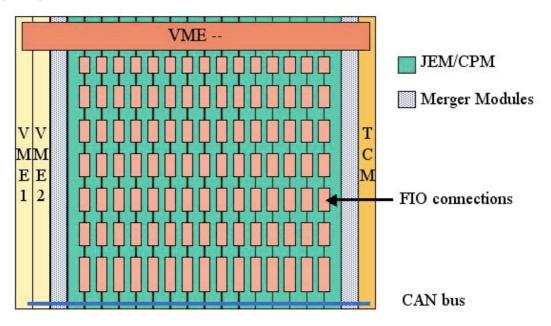

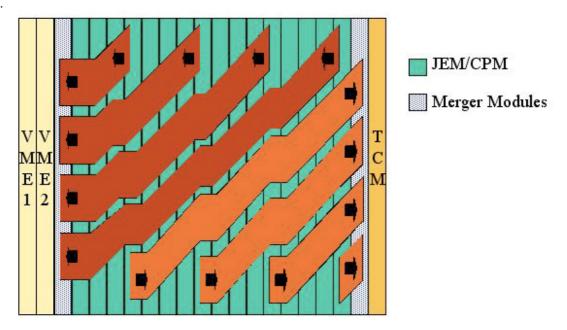

| Table 2: Organization of Processor Backplane layers. Approximate diagrams representing each |

|---------------------------------------------------------------------------------------------|

| type of signal layer are illustrated in Figures 1, 2 and 3.                                 |

| Layer # | Signal types in layer                           | Figure |

|---------|-------------------------------------------------|--------|

| 1       | Chassis ground                                  |        |

| 2       | VME, Geographic address lines, TTC fanout       | 1      |

| 3       | Signal ground                                   |        |

| 4       | VME, Module Fan in/out connections, CAN bus     | 2      |

| 5       | Signal ground                                   |        |

| 6       | Crate merger lines for modules 0, 4, 8, and 12  | 3      |

| 7       | Signal ground                                   |        |

| 8       | Crate merger lines for modules 1, 5, 9, and 13  | 3      |

| 9       | Signal ground                                   |        |

| 10      | Signal ground                                   | 3      |

| 11      | Crate merger lines for modules 2, 6, 10, and 14 |        |

| 12      | Signal ground                                   |        |

| 13      | Crate merger lines for modules 3, 7, 11, and 15 | 3      |

| 14      | Signal ground                                   |        |

| 15      | VME, Module Fan in/out connections              | 2      |

| 16      | Signal ground                                   |        |

| 17      | VME, Geographic address lines, TTC fanout       | 1      |

| 18      | Chassis ground                                  |        |

Figure 1: Conceptual layout of an outside layer of the PB (1 of 2), with VME-- and TTC signal distribution. These layers also contain the bussed geographic address lines (not shown). View from front of crate

Figure 2: Conceptual layout of a fan-in/out (FIO) layer of the PB, with VME-- and CAN buses. Gaps between the FIO connections are reserved for serial input cable connections. View from front of crate. The small rectangular boxes represent large numbers of short FIO connections between adjacent modules.

### 2.2 Printed circuit board

The Processor Backplane is a large, monolithic custom PCB, populated largely with 2mm Hard Metric connectors. It is 399.2mm high and 425mm wide, and is designed to reside in a 9U x 84HP chassis.

The PB thickness is 5.8mm and it contains 8 signal layers, which are separated by 8 signal ground planes. An additional two outside chassis ground planes are provided for input cable shields, giving a total of 18 layers. All traces are stripline. There are no power planes; all power is distributed from bus bars near the bottom of the crate, and brought to the modules via high-current (40A) pins. The signal

distribution among the different layers is shown in Table 2, and conceptual layouts of the different layers are depicted in Figures 1, 2, and 3.

To simplify routing through the 2mm pitch connectors, only one signal line per layer is routed between any two pins. This, combined with the separation of neighbouring layers with ground planes, is expected to reduce cross-talk to negligible levels [4].

Figure 3: Conceptual layout of a merging layer of the PB (1 of 4). View from front of crate.

### 2.3 Connectors

The primary connector choice for the PB is the 2mm Hard Metric (HM) family, specified by the international standard IEC 1076-4-101. The large number of high-speed input and output signals required by the CPM, JEM, and CMM make it necessary to use connectors with high density, good signal characteristics, and high reliability. This connector style provides connections on a 2mm pitch, 5 columns wide and with a choice of connector heights. Ground-return shields are available for both sides of the female (card ) connectors, which make contact with two additional outside columns on the backplane. By using 2mm HM connectors with 5 rows of signal pins plus two dedicated rows of ground pins, a signal density of 20 signals per centimetre of card edge can be attained while maintaining a signal/ground ratio as low as 4:3. The total width of the connectors is 15.4mm, leaving a space of approximately 5 mm between adjacent connectors.

The 2mm HM connector range (IEC 1076-4-101) has also been chosen due to the availability of a halogen-free cable assembly compatible with the IEC 1076-4-101 specification that is suitable for carrying high-speed LVDS data links from the PreProcessor system to the CPMs and JEMs. These cable links are routed to the back of the processor crates and brought to the modules through the backplane using long through-pins and custom-length shrouds. Custom-built B-19 connectors (Table 3) with eight rows of long through-pins are used to achieve the desired pin configuration. These connectors have three mating levels on the front side to reduce the maximum insertion force.

The modules each consume up to 25 Amperes of 3.3V and 5V DC power. The 2mm HM family includes connectors with DIN cavities that accommodate high-current power pins (up to 40 Amp/pin), which more than suit the system requirements. Tyco/AMP also produces a guide-pin assembly compatible with the 2mm HM family. This assembly helps ensure alignment during board insertion, thus reducing insertion force and minimizing the risk of damage to the PB from improper insertion.

The PB also includes three connectors that do not belong to the 2mm HM family. In each CPU position is a 160-pin VME64-standard J2 connector with through-pins to accommodate eventual daughter cards behind the backplane. There is also a standard 9-pin male DSUB connector behind position 21 to accommodate a standard external CANbus cable

|   | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|

| Z | С | С | С | С | С | С | С | С | С | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  |

| A | В | В | В | В | В | В | В | В | В | С  | R  | R  | R  | R  | R  | R  | R  | R  | В  |

| B | В | В | В | В | В | В | В | В | В | С  | R  | R  | R  | R  | R  | R  | R  | R  | В  |

| С | В | В | В | В | В | В | В | В | В | С  | R  | R  | R  | R  | R  | R  | R  | R  | В  |

| D | В | В | В | В | В | В | В | В | В | С  | R  | R  | R  | R  | R  | R  | R  | R  | В  |

| E | В | В | В | В | В | В | В | В | В | С  | R  | R  | R  | R  | R  | R  | R  | R  | В  |

| F | С | С | С | С | С | С | С | С | С | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  |

Table 3: Pin configuration of custom B-19 connector for CPM/JEM positions

Key (Front / Rear) : B: 6.8 / 0 C: 8.3 / 0 R: 5.3 / 8.25 Note: Estimated pin lengths with shroud and PCB thickness subtracted

### 2.4 Backplane connections

#### 2.4.1 Serial link inputs

Serial link data inputs to the CP and JEP system will be brought to the back side of the backplane via untwisted shielded pair cable assemblies from the PreProcessor system. The current baseline solution for these assemblies are commercially assembled Z-Pack HM assemblies from AMP. Each assembly contains 2 or 4 differential input pairs, plus 1 additional ground shield per two differential cables. While the 4-pair cable assemblies will be used in most cases, the 2-pair assemblies may be required for data at large  $\eta$ , where the calorimeter granularity becomes coarser.

To isolate the high-speed LVDS signals from potential sources of noise, the cable inputs are arranged in blocks of 4 cable assemblies (16 pairs), with ground (or inactive geometric address) pins between the LVDS signals and any other signal pins. The cable ground shields, connected to the middle row of contacts, are connected to the PB chassis ground.

### 2.4.2 Data fan-in/-out

Both the CPM and JEM share their input data with neighbouring modules, to provide each module with a complete environment for cluster and jet identification algorithms. This is done using short point-to-point, unidirectional fan-in/out (FIO) links between modules. Each CPM uses 320 FIO links at 160 Mbit/s, while the JEM uses 330 FIO links at 80 Mbit/s.

The FIO pins occupy the majority of the processor card edge. They have been placed according to the following guidelines to preserve signal integrity and minimise cross talk at 160 Mbits/s:

- Each FIO pin is adjacent to at least one ground pin.

- Blocks of FIO pins contain even numbers of FIO pins (to balance input and output)

- FIO signals leaving a processor module should arrive at the neighboring module on a pin no than one row above or below the source pin. This simplifies layout and reduces FIO routin more g to two signal layers.

#### 2.4.3 Real-time results merging

Each processor module sends its real-time output to two merger modules (CMMs) via unidirectional, single-ended point-to-point backplane links from two 25-bit output ports, one at the top and one at the bottom of the module. Each CMM therefore receives level-1 real-time results from up to 16 processor modules, each with a width of 24 data bits and one bit of parity. The merger signals are routed diagonally from the processor modules to the CMMs using four signal layers.

#### 2.4.4 Timing, trigger and control (TTC) distribution

A timing and control module (TCM) in each crate receives the 160 Mbit/s TTC signal via an optical fibre, and distributes it electrically to all other modules in the crate as differential PECL signals in a

star configuration. The electrical signals are sent along pairs of parallel  $50\Omega$  lines to produce the equivalent of a  $100\Omega$  differential impedance.

#### 2.4.5 CAN bus

The TCM also provides the interface between the crate and the ATLAS Detector Control System (DCS). A differential CAN bus is provided to all modules in the crate, and allows readout of temperature and supply voltage information through the TCM to the DCS. A 9-pin D-sub connector is also provided in the rear of the PB to allow a standard CAN cable to be connected to the bus for monitoring and diagnostics. The CAN bus is terminated at position 21 on the TCM. Termination at position 1 is provided on the VMM.

Power for the CAN controller comes from the 5V crate supply to the TCM. No specific provision is made for an auxiliary +5V CAN power supply.

#### 2.4.6 Reduced VME bus

A commercial VME crate processor (CPU) is used for configuration and control of the CP and JEP subsystems. To economise on signal pins, the CPU interface with the processor modules is over a custom, compact bus, called "VME--", which carries only a subset of the full VME64 standard.

| Signal name      | Number of pins |  |

|------------------|----------------|--|

| SYSRESET         | 1              |  |

| A[231]           | 23             |  |

| D[150]           | 16             |  |

| DS0*             | 1              |  |

| Write*           | 1              |  |

| DTACK*           | 1              |  |

| Total pins used: | 43             |  |

#### Table 4: VME-- signal pins.

The CPU is carried on a 9U by 400mm VME Mount Module (VMM), which can be inserted in slot 1 or 2 of the PB. The VMM receives +5V through the high-current power connectors at the bottom of the board, and is connected to the VME-- bus via a 2mm HM connector. A VME64 standard J2 connector is also provided with thru-pins for mounting adaptor boards in the rear of the crate. While it is not currently foreseen for two VME masters to function in the crate at once, signal lines are provided on the J1 connectors between these two positions for carrying the bus grant, request and status signals BGIN\*(3:0), BGOUT\*(3:0), BR\*(3:0), BBSY\* and BCLR\*, as well as the interrupt chain signals IACK\*, IACKIN\*, IACKOUT\*, and IRQ\*(7:1), should they be needed.

Termination on both ends of the bus is provided on the modules. The VMM in position 1 should provide termination as near as possible to the bus transceiver buffer chips. Termination in position 21 is provided on the TCM.

#### 2.4.7 Geographic addressing

Dedicated address pins on the Processor Backplane provide every module in the CP and JEP subsystems with the information to uniquely determine their position in the system, and accordingly select appropriate VME, CAN, and TTC addresses. Some modules also load different FPGA configurations based on their geographic address.

Three bussed address lines with switches are needed to identify the system (CP or JEP) and crate number (up to 4 crates). Each module requires up to four additional pins to uniquely identify its position within the crate. Table 5 lists the assignments of geographic address pins to the different modules in the crate. Note that only two bussed address pins are necessary for the CPMs and JEMs, since they "know" which system they are in. The TCM requires three address pins to determine which processor crate it is in. The addresses encoded by local address pins for each type of module in the crate begin with 0, and increase sequentially in the order of increasing position number (left to right).

#### Table 5: Geographic Addressing.

| Module Type         # of bussed crate address pins         # of local address pins |

|------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------|

| СММ     | 3 | 1 |

|---------|---|---|

| CPM/JEM | 2 | 4 |

| ТСМ     | 3 | 0 |

The geographic address pins are specified as active high. Their values are set by either connecting them to the backplane signal ground (0), or by leaving them unconnected (1). To provide usable geographic addresses on the modules, these pins are connected to pull-up resistors on the modules. Local address pins can be pulled up to any desired voltage, while the bussed crate address pins must be pulled up to 3.3V, using resistor values of at least 10 k $\Omega$ . An error in the prototype backplane caused the bussed crate-id address pins to be active low, and the local address pins active high. For the final system, a uniformly active high convention is desired. A rotary decade switch with complementary encoding will be used to achieve this.

#### 2.4.8 Power distribution

The processor crates supply regulated +5V and +3.3V power to high-current bus bars, which in turn provide power to each module in the crate. Other voltages needed by a module may be derived locally from the +5V supply. Each module is supplied with three high-current power pins that carry +5V, +3.3V and ground return from the local bus bars. Each backplane power pin is rated at up to 40A, providing a substantial safety margin for all modules in the system.

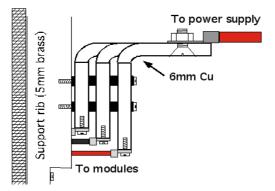

Figure 4: Cross section of power bus bars (not to scale). The bus bars run along the entire width of the PB, and distribute 3.3V, 5V, and signal ground to all modules. Two horizontal tabs on each bus bar accept cables from the crate power supply. The bus bars are mounted on the vertical support ribs. Insulating layers (Plexiglas and Delrin) between and outside the bus bars are included, but not shown in this drawing.

### 2.5 Line impedance

The Processor Backplane must carry a large number of high-speed digital signals, some for long distances, with minimal distortion, reflection, or cross talk. Single-ended signal lines should have an impedance of  $60\Omega$ , while differential signals should be implemented using pairs of parallel lines with  $100\Omega$  differential impedance. To simplify routing and make it easier to achieve the desired differential impedance, the prototype backplane simply routed differential traces as two single-ended lines with 2mm between them, with each trace having a  $50\Omega$  impedance. The VME-- bus is drawn using  $60\Omega$  traces, but the large number of vias connected along it brings the impedance of that bus down to approximately  $50\Omega$ . For the prototype backplane, all  $50\Omega$  lines were drawn using 0.008" traces, and  $60\Omega$  lines were drawn using 0.006" traces, corresponding to widths of approximately 0.007" and 0.005" after the etching process. The backplane manufacturer is responsible for controlling the final impedances. All line impedances are specified to have a tolerance of  $\pm 5\%$ .

### 2.6 Mechanics

The Processor Backplane must be able to withstand repeated insertion and extraction of 9U-height boards with high-density connectors. It is reasonable to expect the number of module insertions/extraction cycles over the lifetime of the backplane to meet or exceed the minimum connector lifetime of 250 such cycles per position (at least for test rigs). Excessive flexing of the backplane during module insertion and extraction can compromise contacts between signal lines and

vias. Flexing also causes connector pin misalignment, which significantly increases insertion/extraction force, thus resulting in even more severe flexing.

To minimize flexing and the problems that it causes, the following measures have been taken:

- An 18-layer backplane PCB with 5.8mm thickness is used. The unusually thick PCB with its many ground planes provides substantial rigidity.

- Custom built B-19 connectors make up the majority of the connector height in the 16 central JEM/CPM positions. These connectors are built with three mating levels which reduces the insertion force in those positions by a few percent.

- A guide pin at the top of each module ensures correct alignment during board insertion, reducing both insertion force and the chance of damage from incorrect alignment.

- Six 20mm-deep vertical support ribs of 5mm-thick brass mounted on the back side of the PB provide a substantial amount of extra stiffness to the PCB, and additionally serve as mounting points for the power bus bars and the input cable strain relief assembly.

### 2.7 Grounding

The processor crates require two grounds: a chassis ground for terminating the cable shields of the LVDS serial links from the PreProcessor system, and a signal ground for local signals within the crate. Since the PreProcessor to CP/JEP connectivity is many-to-many, the proposed grounding scheme for the final system is for all cable shields to be connected to a common chassis ground in each CP/JEP crate, while in the PreProcessor a passive filter between the cable shields and that chassis ground breaks any potential chassis ground loops. To avoid common mode noise in the LVDS links, the chassis and signal grounds in the CP/JEP crates are connected through a resistor. The Processor Backplane is designed to implement this scheme, with some flexibility in how it is done.

The Processor Backplane contains 8 connected signal ground planes separating the different signal layers, and two outside chassis ground planes. The ground return shields and signal grounds of the modules are connected to the PB signal ground planes, while the LVDS cable shields are connected to the chassis ground is also electrically connected to the crate and support ribs.

The connection between the chassis and power grounds can be implemented in several ways. Two large vias (ca. 3mm diameter) near slot 1 of the PB can be used for a single-poing conection between the signal and chassis grounds. These vias can also be used for connections with the power bus bar grounds, or the crate. The CPM and JEM also have the possibility to connect signal and cable grounds on those modules, if a multi-point ground connection proves more useful.

### 2.8 Environmental conditions

The Processor Backplane must be able to tolerate the following environmental conditions:

- 1. Storage temperature: -20°C to +85°C

- 2. Operating temperature:  $0^{\circ}$ C to  $+70^{\circ}$ C

- 3. Relative humidity: 20% to 70%

These tolerances are similar to those required for other components in the Level-1 calorimeter trigger, and are included in the requirements on the manufacturer.

### 2.9 Backplane-to-module pin assignments

The detailed backplane pin assignments for each module are presented in Appendices A through D. All pin assignments are specified according to IEC 1076-4-101, with column A on the left side of the connector and row 1 at the top when viewed from the front. These appendices were used as the authoritative reference both for the backplane and module schematics.

#### 2.9.1 CPU

The PB has two CPU interfaces in positions 1 and 2, as presented in Appendix A. The pin naming follows the following conventions:

| VME***            | VME bus connections                                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| BG*(3:0)(IN/OUT), | Bus grant signals for determining the priority of the VME masters on the                                                             |

| BR*(3:0),         | bus. The bus grant inputs are held low in position 1, and the BG(3:0)                                                                |

| BCLR*, BBSY*      | outputs are connected to their corresponding inputs in position 2.                                                                   |

| IACK*,IACKIN*,    | Signals used for interrupt requests between the VME masters.                                                                         |

| IACKOUT*,         | The IACKOUT* pin in position 1 is connected to IACKIN* in                                                                            |

| IRQ*(7:1)         | position 2.                                                                                                                          |

| GEOADDX           | Geographic address pins. GEOADD(6:4) are bussed lines that identify the crate, while GEOADD(0) identifies the position in the crate. |

| CAN+/-            | Differential CAN bus connection.                                                                                                     |

| TTC+/-            | Differential TTC input.                                                                                                              |

| <g></g>           | Ground pins, connected to the PB ground planes.                                                                                      |

Connector 2 provides a standard VME64 J2 connector for use by possible personality modules mounted in the rear of the backplane. In the center row (B), signals A(31:24), D(31:16) and RETRY are bussed between positions 1 and 2. Grounds in row B are connected to signal ground. All other pins have no connection.

#### 2.9.2 CMM

The Common Merger Modules (CMMs) are located in positions 3 and 20 of the PB. The pin assignments for these modules are presented in Appendix B. The pin naming follows the convention:

| P(15:0)_(24:0) | 40 MHz inputs from up to 16 processor modules                                                                                    |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| M_(83:0)+/-    | Through-pins for 84 differential signals routed to a daughter card on the rear of the PB, where inter-crate cables are attached. |  |  |  |  |

| VME***         | VME bus connections                                                                                                              |  |  |  |  |

| GEOADDX        | Geographic address pins. GEOADD(6:4) consists of bussed lines that identify the crate, while the other pins are module specific. |  |  |  |  |

| CAN+/-         | Differential CANbus connection                                                                                                   |  |  |  |  |

| TTC+/-         | Differential TTC input                                                                                                           |  |  |  |  |

| <g></g>        | Ground pins, connected to the PB ground planes                                                                                   |  |  |  |  |

| <cg></cg>      | Cable ground pins, fed through the PB to daughter cards at the rear.                                                             |  |  |  |  |

#### 2.9.3 CPM/JEM

The pin list for the processor modules (CPMs or JEMs), located in positions 4 to 19 of the PB, is presented in Appendix C. The pin naming follows the convention:

| FL(164:0)    | Fan in/out pins between the module and its neighbour on the left.  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------|--|--|--|--|--|

| FR(164:0)    | Fan in/out pins between the module and its neighbour on the right. |  |  |  |  |  |

| SMM(24:0)    | 40 MHz output pins to the CMM on the left side of the crate.       |  |  |  |  |  |

| JMM(24:0)    | 40 MHz output pins to the CMM on the right side of the crate.      |  |  |  |  |  |

| VME***       | VME bus connections.                                               |  |  |  |  |  |

| GEOADDX      | Geographic address pins. GEOADD(6:4) consists of bussed lines that |  |  |  |  |  |

|              | identify the crate, while the other pins are module specific.      |  |  |  |  |  |

| CAN+/-       | Differential CANbus connection                                     |  |  |  |  |  |

| TTC+/-       | Differential TTC input                                             |  |  |  |  |  |

| <g></g>      | Signal ground pins, connected to the PB ground planes.             |  |  |  |  |  |

| <sg></sg>    | LVDS cable ground pins, connected to the PB chassis ground plane.  |  |  |  |  |  |

| +1, -1, etc. | LVDS cable inputs, Implemented as through-pins.                    |  |  |  |  |  |

In position 4, pins FL(164:0) are not tracked, since they would be connected to non-existent modules. Likewise, FR(164:0) are not tracked in position 19.

#### 2.9.4 TCM

The pin list for the TCM, mounted in position 21, is presented in Appendix D. The pin naming follows the convention:

| VME***       | VME bus connections                                                       |  |  |

|--------------|---------------------------------------------------------------------------|--|--|

| GEOADDX      | Geographic address pins. GEOADD(6:4) consists of bussed lines that        |  |  |

|              | identify the crate number.                                                |  |  |

| CAN+/-       | Differential CANbus connection                                            |  |  |

| TTC(20:1)+/- | Differential TTC outputs, sent to modules in positions 1 to 20 of the PB. |  |  |

| <g></g>      | Signal ground pins, connected to the PB ground planes.                    |  |  |

Connector 1 is implemented with long through-pins to accept bus-termination daughter cards.

#### 2.9.5 CANbus connector

A 9-pin male DSUB connector behind position 21 of the PB can be used to connect a standard CANbus cable to the internal bus on the backplane. The connected pins are:

| Pin 2: | CAN_L    | Connected to CAN- on the PB               |

|--------|----------|-------------------------------------------|

| Pin 3: | CAN_GND  | Connected to the PB signal ground planes  |

| Pin 5: | CAN_SHLD | Connected to the PB chassis ground planes |

| Pin 7: | CAN_H    | Connected to CAN+ on the PB               |

All other pins are unconnected on the PB.

### 2.10 Connector numbering and silkscreen

A simple connector numbering convention has been chosen to make locating connectors on the PB as simple as possible. Connector names are in the form Jxxy, where xx indicates the slot number (from 01 to 21) and y is the connector number (from 1 to 9) counting from the top of the PB. On the prototype backplane, the connector names and outlines were included on the front side silkscreen. For the production backplanes, they will be provided on both the front and back sides.

Other additions to the silkscreen for the production PB include:

- Marking selected VME signal pins (DS0\*, WR\*, DTACK\*, RESET\*)

- Improved labelling on the back side to aid in locating connectors and pins.

- A numbering scheme for the cable input shrouds. The shrouds in each JEM/CPM slot are numbered 1 to 6, counting from top to bottom.

## 3 Prototype PB test results

Following the PB preliminary design review (PDR) in 2001, four prototype processor backplanes were manufactured, assembled in crates with prototype mechanics, and distributed to labs in Birmingham, RAL and Mainz for testing and integration of prototype trigger hardware during 2002-2004. A series of tests was carried out in conjunction with the larger testing programme in order to verify all aspects of the PB design. Below are the results of these tests.

### 3.1 Connectivity

The connectivity of the PB is specified in Appendices A through D of this document. These appendices have also been used to specify the backplane pin assignments for all modules interfacing with the PB. To test all backplane connections, test patterns and data have been sent between all modules in all positions. These tests included:

- VME: Modules in all positions can be accessed and configured using the VME-- bus.

- **TTC and CAN:** The TCM provides TTC signals and CAN access to all other modules in the crate. The correct distribution of both of these was tested both experimentally, and by manual inspections of the backplane traces in the artwork.

- FIO: Data fan in/out between processor modules has been verified by running test data patterns between adjacent JEMs (which use all 330 FIO lines between each position) in all 16 processor module positions

- **Merger data:** Random test patterns were sent from CPMs in all 16 processor module positions to each CMM position, where correct reception was tested. For three CPM-CMM connections where firmware problems made this test difficult, all lines were tested and verified by hand. In all other cases, the data were received correctly in the appropriate places.

### 3.2 Impedance

Impedance tests of the backplane traces were carried out both at RAL and Stockholm University.

The RAL tests used a time domain reflection technique to measure the reflection of square pulses at the interface between a 50 $\Omega$  coaxial cable and the backplane traces. The impedance of selected 60 $\Omega$  merger traces were measured to be ~67.5 $\Omega$ , while the impedance of a 50 $\Omega$  TTC trace was found to be ~60 $\Omega$ . The VME-- bus traces were drawn as 60 $\Omega$ , but the large numbers of connected vias along them bring down the measured impedance to roughly 50 $\Omega$ .

The Stockholm tests used a miniature trim-pot at the far ends of selected backplane traces to cancel out reflections, and the trim-pot resistance was then measured with an ohm-meter to give an impedance measurement. The results of these tests were  $58.6\pm2$  ohms for the  $60\Omega$  traces, and  $49.2\pm2.5$  ohms for the  $50\Omega$  traces. Although these results were much closer to the initial specifications, the Stockholm tests do not account for inductive trim-pot impedance at high frequencies, which would reduce the apparent impedance of the trace. Therefore the RAL results are considered more reliable.

For the production PB, 50/60 ohm single-ended impedances will be specified with 5% tolerances, and arrangements will be made with the manufacturer to ensure that these tolerances are met.

### 3.3 Propagation delays

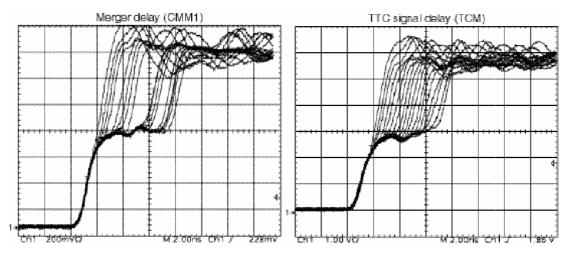

Propagation delay was measured at Stockholm by introducing fast square pulses (rise time  $\sim 2ns$ ) to one end of a signal trace, and leaving the far trace unconnected. The timing of the reflected pulse was compared for merger and TTC signals in each position.

Delay tests of selected merger and TTC signals on the prototype backplane are shown in Figure 5. The delays of the diagonal merger signals from the 16 CPM/JEM positions have a ~3ns spread, while the spread of the TTC signal delays between the 18 CMM and CPM/JEM positions is roughly 2.5ns. This suggests a signal propagation speed of roughly 16cm/ns.

Given the 25ns period of data on the merger lines, the 3 ns spread between all modules yields ample margins for timing in data at the CMM inputs. The average TTC clock difference between neighbouring modules is 0.15 ns, which again gives ample timing margins even for the 160 Mb/s FIO signals. But it is recommended to correct for the TTC propagation delays through proper deskew clock settings.

Figure 5: Reflection measurements of merger signal delays. The combined merger delay plot represents transmitted and reflected pulses from all sixteen CPM/JEM module positions to CMM 1. The corresponding plot for CMM 0 is nearly identical. The combined TTC signal delay plot represents transmitted and reflected pulses from all CPM/JEM and CMM positions to the TCM in position 21. The time scale is 2ns/div, giving a signal transmission time scale of 1 nsec/div.

### 3.4 Cross talk

The Processor Backplane is designed for minimal cross talk. Neighbouring traces on the same signal plane are separated by 2mm, and the signal planes are separated by solid ground planes. Eight signal ground planes provide a strong common ground, minimising any local ground bounce effects. The major sources of cross talk on the backplane are capacitive and inductive coupling between neighbouring traces.

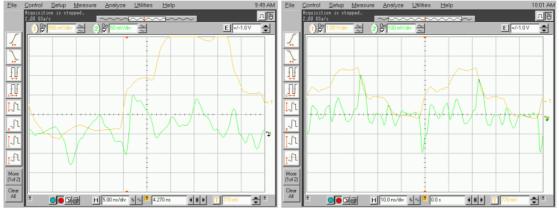

To perform "worst case" tests of cross talk between backplane signals, test patterns were developed to synchronously toggle large numbers of backplane signals while holding a few "test" lines constant. An oscilloscope was used to measure the amplitude of the cross talk on those lines.

Figure 6: Measured cross talk between merger data lines for a CPM slot next to the CMM (left) and one on the opposite side of the crate from the CMM (right). The time and vertical scales for the cross talk signals (green) on the left and right plots are 5ns/50mVand 10ns/100mV per division, respectively. The vertical scales for signals on the adjacent lines (yellow) are 100 times greater than the cross talk traces.

### 3.4.1 Merger-Merger cross talk

The greatest expected cross talk is expected to occur on the long merger data lines between the processor modules and the CMMs. To distinguish the "near end" and "far end" components of the cross talk, two tests were performed, one for a CPM adjacent to a CMM, and another near the opposite end of the crate. The results of these two tests are illustrated in Figure 6.

The case where the CPM was adjacent to the CMM is mainly a test of "near end" cross talk (NEXT), which was measured to be less than 5%. The case where the CPM was at a maximum distance from the CMM provided a worst-case test of "far end" cross talk (FEXT). The characteristic pulse at the rising and falling edges of the adjacent arriving signals was less than 10%. This provides ample margin for digital signal integrity. The polarity of the FEXT pulse was the opposite of the rising/falling edges of the driving lines, indicating that the inductive coupling between merger lines is greater than the capacitive coupling.

### 3.4.2 FIO-LVDS cross talk

The 400 Mbit/s input data links have some sensitivity to common-mode noise, so it was important to investigate the worst-case scenario for FIO noise affecting the input links. To do this, three CPMs in adjacent slots were used, with LVDS data sent from data source/sink modules to all input channels of the center CPM. Synchronous "AA" patterns were sent to the center CPM via the LVDS, and loaded into the playback memories of the neighbouring CPMs, so that all of the FIO lines on all three modules transitioned continuously and simultaneously at 160 Mbit/sec.

This pattern was intended to surround the LVDS links with the largest possible number of simultaneously transitioning signals. After several minutes of running, no parity errors were observed on any of the LVDS links, setting a worst-case upper limit on the bit-error rate at  $\sim 10^{-13}$ . An attempt was made to measure any local ground bounce due to this worst-case test pattern. The absence of an independent local reference ground made it impossible to measure this exactly, but a generous upper limit of 100 mV was obtained, which is well within the tolerance of the LVDS receivers. The true ground bounce amplitude is probably much smaller than this limit.

#### 3.4.3 VME–Merger cross talk

Another potential source of cross talk comes from the VME-- bus, which employs higher-current drivers than other signal sources. There was a concern that VME cycles occurring during data taking might affect signal quality on other signal lines, especially longer lines with large capacitive couplings to the ground planes. To test this, a repeating signal was driven on selected long merger lines while the VME was used to read and write to module addresses in the crate. A sample measurement is shown in Figure 7.

Figure 7: Measured cross talk between the VME bus and merger lines. The DTACK signal (yellow) is asserted at the end of a VME cycle. A repeating signal on one of the longest data merger lines (green) is unaffected by the VME activity. The time scale is 50 ns/div, and the vertical scale is 1.0 V/div for both traces.

Activity on the VME-- bus was found to have no measurable effect on the merger data. This can be attributed to the fact that the merger and VME-- lines are located on different signal layers, and the large number of ground planes minimizes any ground bounce effects. Furthermore, the VME-- bus will be driven with 3.3V signals in the production system, further minimising potential cross talk issues.

#### 3.4.4 Full system tests

To verify that a fully populated processor crate will function properly, a system integration test was performed with six CPMs, two JEMs, two CMMs and a TCM in a single crate. The processor modules ran preprogrammed test patterns on the FIO links between them, as well as data to both CMMs. At the same time, the VME bus was exercised heavily through continuous reading and writing of the dual port RAM of the TCM.

After two hours of continuous operation, no errors had been seen at the CMM inputs, corresponding to a bit-error rate of less than  $10^{-13}$ . This test provides further confidence that the backplane has no serious cross talk or ground bounce issues that threaten data integrity.

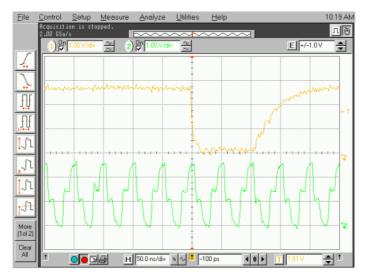

### 3.5 TTC signal quality

The 160 Mbit/sec TTC signal, distributed differentially by the TCM to each module in the crate, must have a very high signal quality in order to provide low-jitter clocks to the system. To test this, a JEM was inserted in slots 4 and 19, corresponding to the lowest and highest processor module distances from the TCM. A high L1A rate (ca. 130k/sec) was transmitted on the A channel to make the TTC signal less deterministic, and possibly introduce more potential instability. A differential probe measured the TTC signal at the JEM position, and a commercial program (Tektronix) was used to calculate the jitter of this signal.

There was no noticeable degradation of the TTC signals from the short to the long TTC tracks on the backplane. The jitter of these signals appeared to depend on the driver channel from the TCM, and the data time interval error (TIE) of these signals had RMS values as low as ~37 ps.

### 3.6 Power distribution

The prototype processor crates distributed 5V and 3.3V power to all modules in the crate using 1 cm<sup>2</sup> horizontal copper bus bars mounted by insulating holders to the sides of the card cage. The power pins in each slot were connected to the bus bars using short AWG8 cables. This configuration provided excellent current carrying capabilities, but make backplane removal or power pin replacement extremely difficult.

A new power distribution scheme (Section 2.4.8) has been adopted for the production crates. The bus bars have even larger cross sections, and are mounted to the backplane support ribs (Appendix I). The wires between the bus bars and the power pins are thinner (2.5 mm<sup>2</sup>), but can be made less than 5cm long. The resistance of these connections at high currents (up to 24A) was measured to be ~1.3 m $\Omega$ , which will result in minimal power drops between the bus bars and the modules (less than 25 mV on the CPM). Voltage fluctuations at the module power inputs due to changing load conditions should be negligible.

### 3.7 Mechanics

The vertical support ribs described in Appendix I are primarily designed to minimize flexing of the backplane PCB during module insertion and extraction. For the prototype processor crates, four aluminium ribs per crate were used. This reduced the maximum displacement from flexing to less than 1mm, resulting in a significant reduction of the insertion and extraction forces. For the production crates the number of ribs will be increased to six, and they will be made of brass instead of aluminium. This should provide even more rigidity, and further reduce insertion and extraction forces.

The most significant mechanical problem seen in the prototype tests was the integrity of the insertion/extraction levers on the module front panels. The front panel hardware for the processor crates is specified by IEEE 1101.10, which includes handles with "hooks" that fit in to the front extrusions and provide leverage for insertion and extraction. On a number of prototype modules, excessive wear was found on these hooks, rendering the handles ineffective. The cause of the problem was found to be vertical flexing of the crate extrusions during insertion, which prevented the hooks from properly engaging. For the production crates, additional reinforcement will be provided to reduce to reduce flexing of the front extrusions. High-quality handles that satisfy the IEEE 1101.10 specifications should also be specified for all production modules. These should be made either of durable plastic (e.g ELMA 81-077/81-078) for modules with low insertion force (VMM and TCM), or preferably solid aluminium (available at www.tripleease.com).

### 3.8 Module keying

In total, there are five different types of modules (VMM, CMM, CPM, JEM, TCM) that are designed to be inserted in the PB, and each module must be inserted only in the positions designated for it. No keying scheme was used in the prototype crates to prevent inserting modules in incorrect positions (for example, a CPM in a CMM slot). This is clearly undesirable for the final system. Module keying tabs (from e.g. ELMA) can be installed near the front of the crate and behind the module inject/eject handle assemblies that can stop misplaced modules before they make contact with the PB. Such a solution is foreseen for use in the final system.

### 3.9 Repair and maintenance

The 2mm HM connector family can suffer damage in the form of bent or broken pins, and a method for field repair is essential for maintaining the processor backplane over the lifetime of the ATLAS experiment.

Several backplane pins have been bent or broken during the prototype testing and integration period. In the case of minor bending, the pins can be straightened again without any noticeable problems. However, severely bent pins must be replaced. Tyco/AMP sells a 2mm HM field repair kit (part number 354687-1). This kit has been successfully used for pin replacement on the prototype backplane, and is considered suitable for field replacement of damaged pins. More serious damage

involving a large number of pins will require the backplane to be dismounted and sent to an external company for connector replacement.

### 3.10 Errata

Comprehensive tests of the prototype backplanes yielded very good results, and the prototypes could be used in the final system if needed. However, a small number of errors were discovered, and these will be rectified in the production series.

#### 3.10.1 PCB errors

- The geographical address pin GEOADDR0 in slot 20 (CMM1) was inadvertently grounded, yielding an incorrect address for that position. The problem was solved for the prototype PB by removing the offending pin. The error in the PB schematics has been identified and corrected.

- The 9-pin male DSUB connector for external access to the CAN bus in slot 21 had the CAN+ and CAN- signals reversed. This will be corrected in the final revision.

- The rotary switch for the crate address resulted in an active low crate ID, while the other geographic address lines are active high. This has been compensated in the prototype design by firmware modifications, but the rotary switch will be replaced with one with complementary encoding in the final design.

- The bus grant and interrupt lines between the two CPU positions were incorrectly implemented in the prototype. The following changes are implemented in the final revision to conform with VME specifications:

- All BGXIN\* signal pins in slot 1 are left floating.

- All BGXOUT\* pins in slot 1 are connected to BGXIN\* in slot 2.

- IACKOUT\* in slot 1 is connected to IACKIN\* in slot 2.

- IACKIN\* and IACK\* are connected together in slot 1.

Another issue with the prototypes was the lack of access to the chassis ground over the back side of the backplane. Pads for 84 surface mount test points connected to chassis ground are provided in the production design.

#### 3.10.2 Mechanical issues

- The cable headers in slots 4-19 had 7 rows (5 signal plus 2 ground). This was found to interfere with the chosen cable connector. The final connectors for these positions have only five rows of long through-pins.

- The shrouds for the cable headers in slots 4-19 were polarised. However, the polarisation was insufficiently strong to ensure correct cable orientation, and the available polarised shrouds had durability issues. The shrouds for the production backplanes have therefore been specified as unpolarised. A visual system for ensuring correct cable orientation (e.g. paint spots on the connector) is necessary, and should be sufficient.

- The two CMM slots (3 and 20) have two types of connectors with long though-pins and shrouds for accepting the Rear Transition Module (RTM), which provides remote cable connection to the CMM. Due to an oversight in specification, the prototype backplanes were delivered with connectors in these positions that had different through-pin lengths, as well as different shroud thicknesses. The combined effect of these differences was that some of the RTM pins had a very short usable length, and the RTM needed to be modified to correct for this. The production backplane will have stricter specifications on the pin length and shroud thickness for connectors in these positions.

- The bottom-most connectors in the CPU and TCM slots had long through-pins and shrouds in the prototype, to allow use of yet-unallocated pins in those positions. No use has yet been found or proposed for these pins, and in practice these long through-pins and shrouds were easily damaged and/or obstructed. They will therefore be removed in the production version.

- The bottom-most cable headers (on connector 7) in slots 4-19 are half populated with LVDS input pins. The other pins are used for FIO signals and signal grounds. In the prototype backplane all of these pins mated with the input LVDS cable, making it possible for the FIO signals to be connected to long, unused cables. To avoid this in the final design, the pins for these FIO signals must be clipped.

## 4 Project management

### 4.1 Overview and deliverables

The PB serves both the CP and JEP systems, and naturally must be compatible with all other components in these two systems. Several of these components have already been specified and reviewed, so this specification tries to embody the requirements of those components, as well as to anticipate the requirements of the components yet to be reviewed

This document specifies the production processor backplane of the Level-1 Calorimeter Trigger. Production will be completed in 2005, and installation at ATLAS will be complete by 2006.

The deliverable products of this phase of the project are:

- Specification (this document).

- 11 production PBs (6 system crates plus 1 spare crate for ATLAS, 3 test rigs, and 1 spare PB).

- Support and cable strain relief hardware for 14 crates (production plus prototype)

- Power bus bar assemblies and custom sense wire cards for 10 production crates.

- PB User Reference Guide (This document, suitably modified, may be sufficient).

- Design documentation (schematics, layout information, component data-sheets etc.)

### 4.2 Personnel

The PB is one of the main hardware responsibilities of the Stockholm group and has been designed there. The main personnel for the project are named below, supported by other members of the Level-1 Calorimeter Trigger Collaboration:

Project Management: Samuel Silverstein (Stockholm) Project Engineering: Samuel Silverstein, Christian Bohm (Stockholm)

### 4.3 Design and verification

The design of the PB will be done in Stockholm. The schematic design and layout will be carried out using Mentor Graphics electronics CAD software.

### 4.4 Manufacturing

The PCB layout and routing will be performed by Stockholm, which will also supervise the manufacture and assembly of the PB. An external company specialising in backplane manufacture and connector fitting will be consulted, and carry out the final PB manufacture and assembly.

The manufacturer will be responsible for PCB production, ordering parts (except for custom parts, which will be the responsibility of Stockholm University), assembly, and testing.

Additional mechanical components including the support ribs, cable strain relief, CMM rear transition module guides, and power bus bars, will be engineered and manufactured in Stockholm. Stockholm University will also receive all production crates from CERN, modify them, and install the backplanes and other hardware before shipping them to their final destinations.

### 4.5 Pre-production testing

The manufacturer will produce an initial pre-production PCB and test it for connectivity and short circuits. A visual inspection of the board, as well as impedance testing of selected signal lines will be carried out to verify that the PCB meets the specifications

Once it has been established that the PCB fulfills all specifications, the remaining ten backplane PCBs may be produced. The manufacturer is responsible for testing of connectivity/shorts and impedance of selected lines. The test data for each PCB will be made available to Stockholm.

The pre-production backplane will then be assembled by the manufacturer, and the assembled PB will be completely tested for connectivity and short circuits. Stockholm University will perform a final

visual inspection of the completed backplane, and resolve any issues with the manufacturer, before assembly of the remaining PCBs is authorized.

### 4.6 Production testing

Once the pre-production PB has been completed and verified, the manufacturer will then be asked to produce, assemble and test 10 production backplanes.

For the production run, the manufacturer will be responsible for testing the bare PCBs and assembled backplanes for connectivity, short circuits and selected line impedances. Stockholm University will perform additional inspections of the delivered backplanes before finally installing them with associated hardware in the production crates.

### 4.7 Costs

Detailed cost information for the production PB is not yet available. Preliminary specification documents and artwork will be provided to prospective manufacturers to enable an accurate cost estimate to be obtained

## 5 Production and distribution

The following approximate milestones are expected for production and distribution:

| Dec 2004      |

|---------------|

| Jan 2005      |

| February 2005 |

| April 2005    |

| May 2005      |

|               |

## 6 Summary

We have presented the specification for the production Processor Backplane for use by the ATLAS Level-1 Calorimeter Trigger. It has evolved from the prototype design with few changes, and tests of the connections, signal quality and mechanical characteristics of the prototype have yielded good results.

## Glossary

| РВ               | Proceesor Backplane; the component specified in this document |  |  |

|------------------|---------------------------------------------------------------|--|--|

| СР               | Cluster Processor sub-system of the Calorimeter Trigger       |  |  |

| JEP              | Jet/Energy Processor sub-system of the Calorimeter Trigger    |  |  |

| СРМ              | Cluster Processor Module, main module of CP system            |  |  |

| JEM              | Jet/Energy Module: main module of JEP subsystem               |  |  |

| Processor module | Refers to either the CPM or JEM                               |  |  |

| СММ              | Common Merger Module                                          |  |  |

| VMM              | VME Mount Module. Hosts a VME CPU in positions 1 or 2.        |  |  |

| ТСМ              | Timing and Control Module                                     |  |  |

| TTC              | Timing, Trigger and Control                                   |  |  |

| DCS              | Detector Control System                                       |  |  |

| LVDS             | Low-Voltage Differential Signalling                           |  |  |

| U                | Unit of module height, 1U equals 1.75"                        |  |  |

| HP               | Unit of module width, 1HP equals 0.2"                         |  |  |

### References

- 1. ATLAS First-level trigger technical design report (TDR), CERN/LHCC/98-14.

- 2. IEC Standard 1076-4101

- 3. IEEE Standard 1101.10-1991

- 4. ATLAS Level 1 Calorimeter Trigger Simulation of the backplane for the Common Merger Module. Jayananda, M K, ATL-DAQ-2000-004.

## Appendix A: CPU interface connector layout

| Pos. | А              | В              | С              | D             | E        |

|------|----------------|----------------|----------------|---------------|----------|

| Guid | le Pin (0-8mm) | (AMP parts 2   | 223956-1, 2239 | 957-1, or equ | ivalent) |

| Conn | lector 1 (8-58 | 3mm) Type B-25 | 5 connector (s | short through | -pins)   |

| 1    |                | <g></g>        | VMED00         | VMED08        | VMED09   |

| 2    | BBSY*          | VMED01         | VMED02         | VMED10        | VMED11   |

| 3    | BCLR*          |                | VMED03         | VMED12        | VMED13   |

| 4    | BG0IN* *       | VMED04         | VMED05         | VMED14        | VMED15   |

| 5    | BG0OUT* **     | <g></g>        | VMED06         | VMEA23        | VMEA22   |

| б    | BG1IN* *       | VMED07         | <g></g>        | VMEA21        | VMEA20   |

| 7    | BG10UT* **     | <g></g>        | VMEDS0*        | <g></g>       | <g></g>  |

| 8    | BG2IN* *       | VMEWRITE*      | <g></g>        | VMEA18        | VMEA19   |

| 9    | BG2OUT* **     | :              | VMEDTACK*      | VMEA16        | VMEA17   |

| 10   | BG3IN* *       | VMEA07         | VMEA06         | VMEA14        | VMEA15   |

| 11   | BG3OUT* **     | <g></g>        | VMEA05         | VMEA12        | VMEA13   |

| 12   | BR0*           | VMEA04         | VMEA03         | VMEA10        | VMEA11   |

| 13   | BR1*           | <g></g>        | VMEA02         | VMEA08        | VMEA09   |

| 14   | BR2*           | VMERESET*      | VMEA01         | <g></g>       | <g></g>  |

| 15   | BR3*           | <g></g>        |                |               |          |

| 16   | IACK*          | <g></g>        |                |               |          |

| 17   | IACKIN*        | <g></g>        |                |               |          |

| 18   | IACKOUT*       | IRQ7*          |                |               |          |

| 19   | <g></g>        | IRQ6*          |                |               |          |

| 20   | <g></g>        | IRQ5*          |                |               |          |

| 21   | <g></g>        | IRQ4*          |                |               |          |

| 22   | <g></g>        | IRQ3*          |                |               |          |

| 23   | <g></g>        | IRQ2*          |                |               |          |

| 24   | <g></g>        | IRQ1*          |                |               |          |

| 25   | GEOADD6        | GEOADD5        | GEOADD4        | GEOADD0       |          |

\* Set low in Position 1 (bus master)

\*\* Implemented only in Position 1

Connector 2 160-pin J2 VME64 connector All through pins to rear of backplane for use of personality cards. All labeled pins (except for ground) are connected between positions 1 and 2. Unlabeled pins have no connection.

| Pos: | A | В       | С |  |

|------|---|---------|---|--|

| 1    |   |         |   |  |

| 2    |   | <g></g> |   |  |

| 3    |   | RETRY   |   |  |

| 4    |   | A24     |   |  |

| 5    |   | A25     |   |  |

| 6    |   | A26     |   |  |

| 7    |   | A27     |   |  |

| 8    |   | A28     |   |  |

| 9    |   | A29     |   |  |

| 10   |   | A30     |   |  |

| 11   |   | A31     |   |  |

| 12   |   | <g></g> |   |  |

| 13   |   |         |   |  |

| 14   |   | D16     |   |  |

| 15   |   | D17     |   |  |

| 16   |   | D18     |   |  |

| 17 | D19     |  |

|----|---------|--|

| 18 | D20     |  |

| 19 | D21     |  |

| 20 | D22     |  |

| 21 | D23     |  |

| 22 | <g></g> |  |

| 23 | D24     |  |

| 24 | D25     |  |

| 25 | D26     |  |

| 26 | D27     |  |

| 27 | D28     |  |

| 28 | D29     |  |

| 29 | D30     |  |

| 30 | D31     |  |

| 31 | <g></g> |  |

| 32 |         |  |

#### Connector 3 (292-336mm) Type B-22 connector (short through pins)

| 1  |         |         |         |         |  |

|----|---------|---------|---------|---------|--|

| 2  |         |         |         |         |  |

| 3  |         |         |         |         |  |

| 4  |         |         |         |         |  |

| 5  |         |         |         |         |  |

| 6  |         |         |         |         |  |

| 7  |         |         |         |         |  |

| 8  |         |         |         |         |  |

| 9  |         |         |         |         |  |

| 10 |         |         |         |         |  |

| 11 |         |         |         |         |  |

| 12 |         |         |         |         |  |

| 13 |         |         |         |         |  |

| 14 |         |         |         |         |  |

| 15 |         |         |         |         |  |

| 16 |         |         |         |         |  |

| 17 |         |         |         |         |  |

| 18 |         |         |         |         |  |

| 19 |         |         |         |         |  |

| 20 | <g></g> | <g></g> | <g></g> | <g></g> |  |

| 21 | CAN+    | <g></g> | TTC+    | <g></g> |  |

| 22 | CAN-    | <g></g> | TTC-    | <g></g> |  |

Connector 4 (336-361mm) Type D (N) connector

| 2  | +3.3V     |

|----|-----------|

| 6  | Power GND |

| 10 | +5.0V     |

## Appendix B: CMM connector layout

| Pos.  | A                                                                                                                                | В                | С            | D            | E       |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|--------------|---------|--|--|--|

|       | Guide Pin (0-8mm) (AMP parts 223956-1, 223957-1, or equivalent)<br>Connector 1 (8-46mm) Type B-19 connector (short through-pins) |                  |              |              |         |  |  |  |

| Conne | ector I (8-                                                                                                                      | -46mm) Туре в-19 | connector (s | nort through | n-pins) |  |  |  |

| 1     |                                                                                                                                  | <g></g>          | VMED00       | VMED08       | VMED09  |  |  |  |

| 2     |                                                                                                                                  | VMED01           | VMED02       | VMED10       | VMED11  |  |  |  |

| 3     |                                                                                                                                  | <g></g>          | VMED03       | VMED12       | VMED13  |  |  |  |

| 4     |                                                                                                                                  | VMED04           | VMED05       | VMED14       | VMED15  |  |  |  |

| 5     |                                                                                                                                  | <g></g>          | VMED06       | VMEA23       | VMEA22  |  |  |  |

| 6     |                                                                                                                                  | VMED07           | <g></g>      | VMEA21       | VMEA20  |  |  |  |

| 7     |                                                                                                                                  | <g></g>          | VMEDS0*      | <g></g>      | <g></g> |  |  |  |

| 8     |                                                                                                                                  | VMEWRITE*        | <g></g>      | VMEA18       | VMEA19  |  |  |  |

| 9     |                                                                                                                                  | <g></g>          | VMEDTACK*    | VMEA16       | VMEA17  |  |  |  |

| 10    | <g></g>                                                                                                                          | VMEA07           | VMEA06       | VMEA14       | VMEA15  |  |  |  |

| 11    | P0_0                                                                                                                             | <g></g>          | VMEA05       | VMEA12       | VMEA13  |  |  |  |

| 12    | P0_1                                                                                                                             | VMEA04           | VMEA03       | VMEA10       | VMEA11  |  |  |  |

| 13    | P0_2                                                                                                                             | <g></g>          | VMEA02       | VMEA08       | VMEA09  |  |  |  |

| 14    | P0_3                                                                                                                             | VMERESET*        | VMEA01       | <g></g>      | <g></g> |  |  |  |

| 15    | P0_4                                                                                                                             | P1_0             | <g></g>      | P2_0         | P3_0    |  |  |  |

| 16    | P0_5                                                                                                                             | <g></g>          | P1_1         | P2_1         | P3_1    |  |  |  |

| 17    | P0_6                                                                                                                             | P1_2             | P2_2         | <g></g>      | P3_2    |  |  |  |

| 18    | P0_7                                                                                                                             | <g></g>          | P1_3         | P2_3         | ₽3_3    |  |  |  |

| 19    | P0_8                                                                                                                             | P1_4             | P2_4         | <g></g>      | P3_4    |  |  |  |

Connector 2 (46-84mm) Type B-19 connector (short through pins)

| 1  | P0_9    | <g></g> | P1_5    | P2_5    | P3_5  |

|----|---------|---------|---------|---------|-------|

| 2  | P0_10   | P1_6    | P2_6    | <g></g> | ₽3_6  |

| 3  | P0_11   | <g></g> | P1_7    | P2_7    | P3_7  |

| 4  | P0_12   | P1_8    | P2_8    | <g></g> | ₽3_8  |

| 5  | P0_13   | <g></g> | P1_9    | P2_9    | ₽3_9  |

| 6  | P0_14   | P1_10   | P2_10   | <g></g> | P3_10 |

| 7  | P0_15   | <g></g> | P1_11   | P2_11   | P3_11 |

| 8  | P0_16   | P1_12   | P2_12   | <g></g> | P3_12 |

| 9  | P0_17   | <g></g> | P1_13   | P2_13   | P3_13 |

| 10 | P0_18   | P1_14   | P2_14   | <g></g> | P3_14 |

| 11 | P0_19   | <g></g> | P1_15   | P2_15   | P3_15 |

| 12 | P0_20   | P1_16   | P2_16   | <g></g> | P3_16 |

| 13 | P0_21   | <g></g> | P1_17   | P2_17   | P3_17 |

| 14 | P0_22   | P1_18   | P2_18   | <g></g> | P3_18 |

| 15 | P0_23   | <g></g> | P1_19   | P2_19   | P3_19 |

| 16 | P0_24   | P1_20   | P2_20   | <g></g> | P3_20 |

| 17 | GEOADD5 | P1_21   | GEOADD4 | P2_21   | P3_21 |

| 18 | GEOADD6 | P1_22   | P2_22   | <g></g> | P3_22 |